CVSD算法分析及其在FPGA中的實現

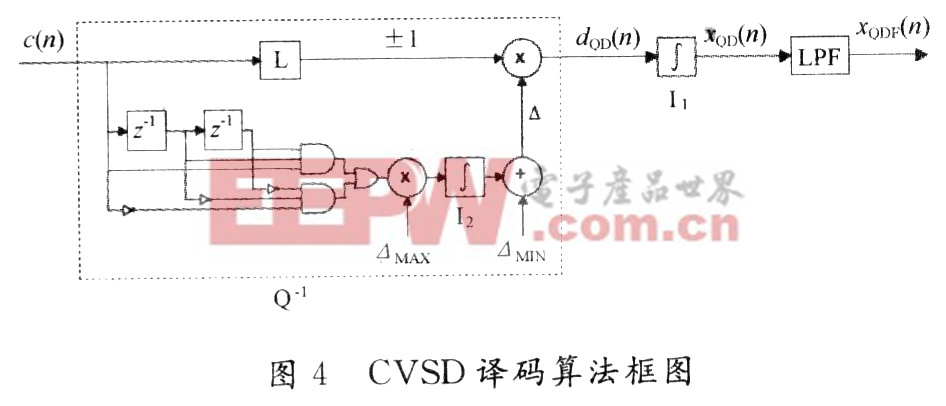

圖4是CVSD譯碼算法框圖,其量階調整是基于前3位的連碼。譯碼過程就是編碼的逆過程,只是在積分器I1后面增加了一個低通濾波器,用于抑制帶外干擾。本文引用地址:http://www.104case.com/article/192064.htm

3 CVSD算法在FPGA中的實現

3.1 硬件實現框圖

考慮到實際需求,采用了通用性較強的A/D,D/A元器件和FPGA器件。該硬件可以同時實現3路CVSD編譯碼算法,一路采用FPGA(XC3S1500)實現,兩路采用專用芯片實現;同時編譯碼之間可以通過FPGA內部邏輯控制互相通信。在FPGA內設計實現了CVSD編譯碼算法,在該器件內融合多種控制功能,可以在線編程、方便調試。

音頻信號在進行A/D采樣之前,為了防止帶外信號進入,首先進行低通濾波;再通過高倍時鐘進行采樣得到數字信號進入FPGA進行編譯碼處理。譯碼過后的信號通過D/A輸出模擬信號,該信號再經過低通濾波器后輸出,得到音頻信號。

3.2 CVSD算法實現框圖

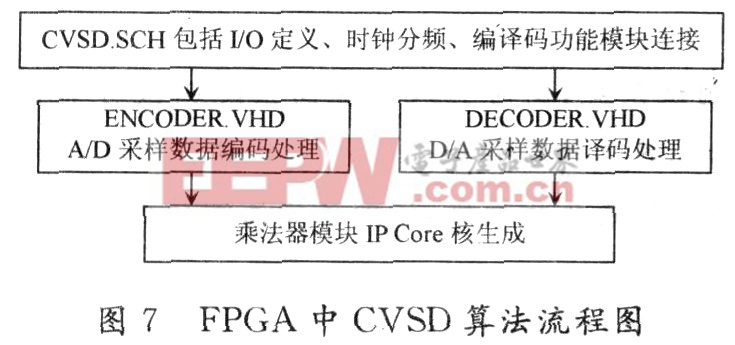

在FPGA內部算法實現上,采用了“自頂向下”的設計方法,即根據要求的功能先設計出頂層的原理圖,該圖由若干個功能模塊組成。再把各個模塊細化為子模塊,各子模塊的功能采用電路圖實現,也可用硬件描述語言實現。設計中頂層采用原理圖實現,子模塊采用VHDL硬件描述語言實現,利用ISE自帶的IP Core乘法器,經過綜合和優化等過程,最終將程序下載到芯片中,使用在線邏輯分析儀ChipScope Pro進行邏輯和功能測試分析。

3.3 CVSD算法的仿真

以正弦單音輸入信號為例,利用信號源產生信號幅度O.5 Vpp,頻率fin(t)=1 kHz的正弦信號作為測試信號,在FPGA中利用高倍時鐘產生fs(t)=64 kHz的采樣時鐘。對輸入A/D的音頻信號采用專用低通濾波芯片進行了濾波。D/A輸出的信號包含了許多不必要的高次諧波分量,因此也采用低通濾波器對其進行了平滑濾波。

評論