基于FPGA的線陣CCD驅動時序電路的設計

O 引 言

電荷耦合器件(Charge Coupled Deviees,CCD)是一種圖像傳感器,它在工業、計算機圖像處理、軍事等方面都得到廣泛的應用。目前CCD的應用技術已成為集光學、電子學、精密機械與計算機技術為一體的綜合技術,在現代光子學、光電檢測技術和現代測試技術領域中起到了相當大的作用。因此,CCD的作用是不可估量的。然而,CCD要正常工作是要驅動時序的,雖然有些CCD往往自帶驅動,但是在特殊需要或需要加特殊功能時,CCD驅動往往需要自己設計,例如曝光時間可調等功能。

現場可編程門陣列(Field Programmahie Gate Array,FPGA)是在PAL,GAL,EPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。

由于FPGA具有易修改,在線編程等特點,可根據不同要求進行在線配置,從而升級方便。另外由于FPGA集成度高,可將系統的部分或全部功能集成在一片芯片上,可減小系統硬件復雜度。

2 CCD工作原理和特性參數

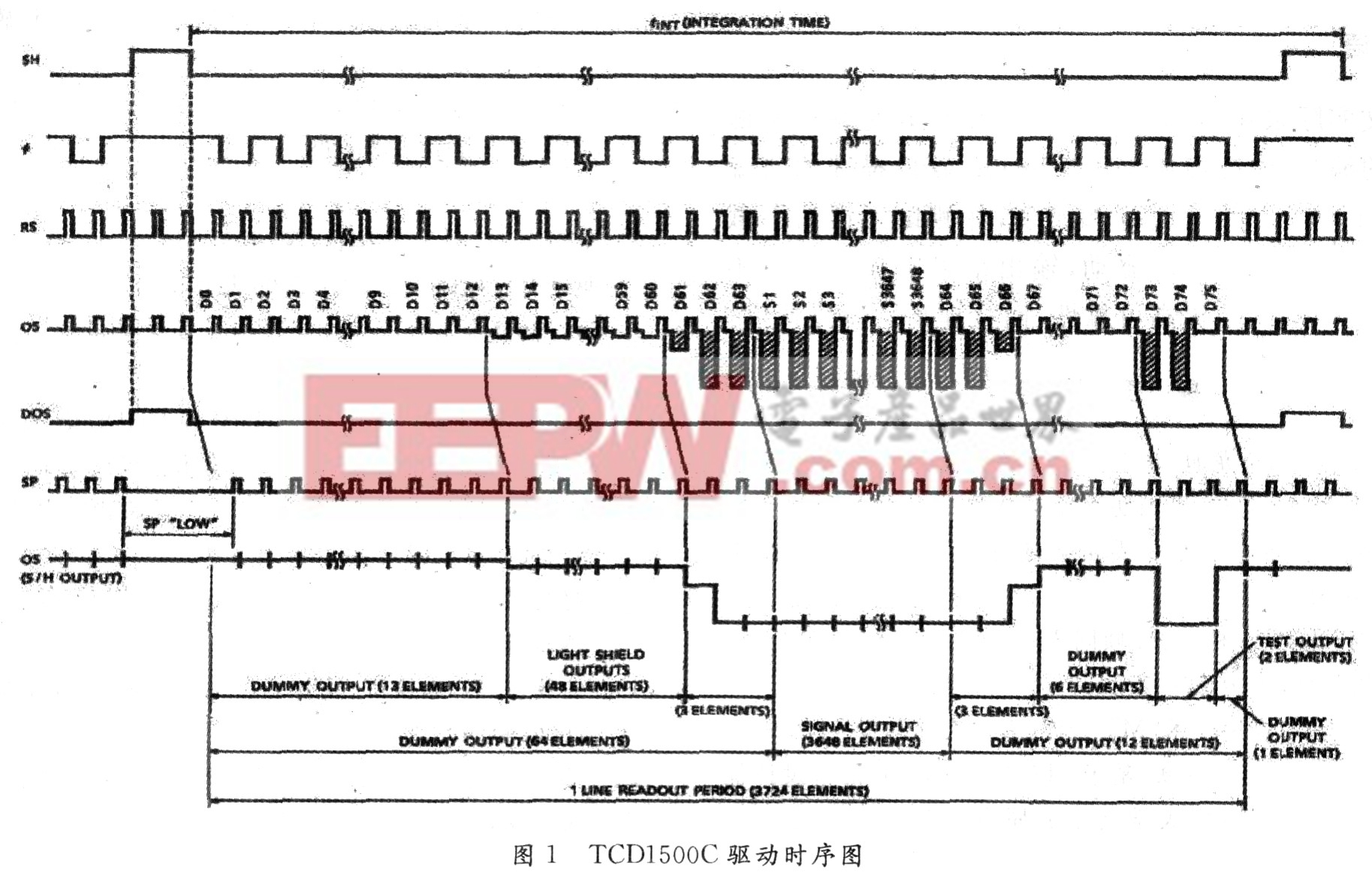

TCDl500C是一種高靈敏度、低暗電流、5 340像元的線陣CCD圖像傳感器,其像敏單元大小是7μm×7μm×7μm;相鄰像元中心距也是7μm;像元總長是37.38 mm。其驅動時序圖如圖1所示。TCDl500C在驅動脈沖作用下開始工作。

由圖1可知,CCD的一個工作周期分為兩個階段:光積分階段和電荷轉移階段。在光積分階段,SH為低電平,它使存儲柵和模擬移位寄存器隔離,不會發生電荷轉移現象。存儲柵和模擬移位寄存器分別工作,存儲柵進行光積分,模擬移位寄存器則在驅動脈沖的作用下串行地向輸出端轉移信號電荷,再由SP進行采樣和保持,最后由0S端分別輸出。RS信號清除寄存器中的殘余電荷。在電荷轉移階段SH為高電平,存儲柵和模擬移位寄存器之間導通,實現感光陣列光積分所得的光生電荷勢阱中,此時,輸出脈沖停止工作,輸出端沒有有效電荷輸出。由于結構上的安排,OS先輸出13個虛設像元信號,再輸出45個啞元像元,然后再輸出5 340個有效像元信號,之后再是12個啞元信號,輸出1個奇偶檢測信號,以后便是空驅動(空驅動的數目可以是任意的)。

2 芯片的選擇以及設計平臺概述

FPGA選擇的是ALTERA公司的FLEXl0K系列的EPFllOKlOLC84一4,他是一款典型在線可編程FPGA器件。

設計選擇的平臺主要是Modelsire。Modelsim仿真工具是Model公司開發的,它支持Verilog DHL,VHDL以及他們的混合仿真,可以將整個程序分布執行,使設計者直接看到它的程序下一步要執行的語句,而且在程序執行的任何步驟任何時刻都可以查看任意變量的當前值,可以在Dataflow窗口查看某一單元或模塊的輸入輸出的連續變化等,比Quartus自帶的仿真器功能強大的多,是目前業界最通用的仿真器之一。仿真都正確無誤后再用QuartusⅡ軟件來綜合和下片。本程序采用Verilog硬件描述語言編寫,其可移植性和可讀性都好。

評論