基于FPGA的線陣CCD驅(qū)動時序電路的設(shè)計

3 CCD驅(qū)動時序的設(shè)計和實現(xiàn)

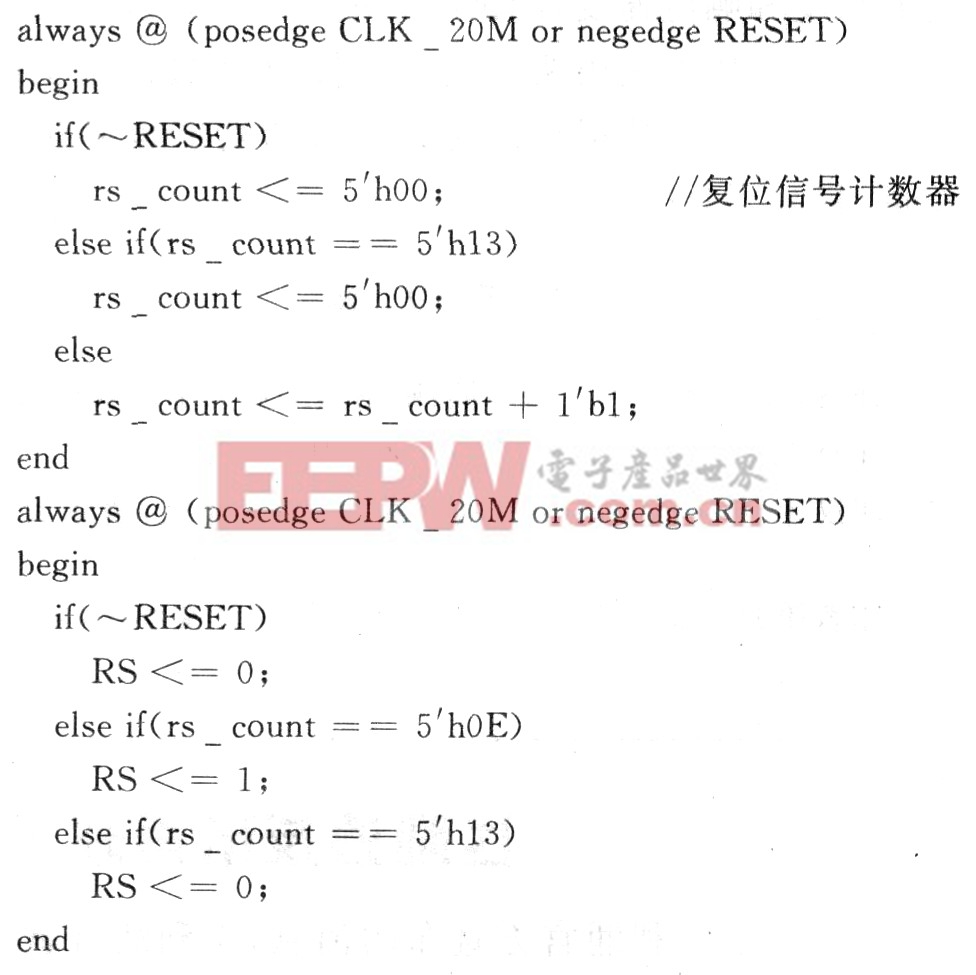

由圖1所示,其設(shè)計方法是:在系統(tǒng)最佳工作頻率下,通過基本計數(shù)單元產(chǎn)生CCD工作所需的波形,保證CCD正常工作。根據(jù)TCDl500C的技術(shù)手冊,可以看出時鐘φ為典型值0.5 MHz時,占空比為1:1;輸出復位脈沖φRS為1 MHz,占空比為1:3,采樣保持脈沖φSP=1 MHz,脈沖寬度為100 ns。根據(jù)所給出的時序關(guān)系圖可以得到轉(zhuǎn)移脈沖φSH,時鐘φ,復位脈沖RS,采樣保持脈沖SP等控制信號的時序圖。由于1個φSH周期中至少要有5 411個φ脈沖,即TSH>5 411T。由此可知,改變時鐘頻率或增加光積分周期內(nèi)的時鐘脈沖數(shù),就可以改變光積分時間。即通過積分時間控制信號A1,A2,A3控制積分時間的改變;000~111分別控制8檔積分時間變換。000時間最短,111時間最長,可以通過軟件動態(tài)設(shè)置積分時間,實現(xiàn)CCD光積分時間的智能控制。部分實現(xiàn)程序如下:

編譯后最后得到的仿真波形結(jié)果如圖2所示。

4 結(jié) 語

本文實際采用Modelsim開發(fā)系統(tǒng)實現(xiàn)編程和測試程序的編寫,內(nèi)部模塊采用Verilog硬件描述語言編寫,完成了時序電路的設(shè)計和實現(xiàn),并測試無誤后下載到FPGA上,產(chǎn)生CCD驅(qū)動,輸出結(jié)果十分理想。不僅簡化了電路設(shè)計,提高可靠性,而且提高了研發(fā)速度。

評論