ADSP TS201鏈路口通信的FPGA實現

子模塊fast控制模塊是由clk,clknot,clkd2和clkd2not四個時鐘組合生成,產生muxO和muxl兩個控制信號。當mux0=0時Datainn(3:O)輸出到DataO,反之,當muxO=1時Datainn(11:8)輸出到Data0;同樣,當muxl=0時Datainn(7:4)輸出到Datal,反之,當muxl=0時,Datainn(15:12)輸出到Datal。

為了提高速度,保證高頻率下程序的穩定性,使用rloc命令,通過對。fast模塊各個觸發器屬性描述及對底層基本邏輯單元的相對位置進行約束,使得同一組數據的觸發器放置相對集中,從而減少了由于時鐘信號在布局布線中產生延遲使得數據建立時間不足而引起的不定態。

3 實現與仿真

ModelSim是一個獨立的仿真工具,在Xilinx公司的ISE集成開發環境中給ModelSim仿真軟件預留了接口,通過這個接口可以從ISE集成工具中直接啟動ModelSim工具進行仿真。由于廠家的推廣,ModelSim得到了廣泛的應用。

仿真也可分為功能仿真和時序仿真等3大類型。由于特殊底層元件的使用,需要一些器件庫模型的支持。而綜合后門級功能仿真以及實現后時序仿真都需要廠家器件庫的支持。

因此,在使用ModelSim 6.2進行功能級仿真和布局布線后仿真時,應根據需要提前對Xilinx的UN ISIM,XmnxCoreLib,SIMPRIM,SmartModel庫進行編譯。其中,UNISIM庫包含了Xilinx公司全部的標準元件;XilinxCoreLib則包含了使用Xilinx CoreGenerator工具生成的IP的仿真模型;SIMPRIM庫用來做時序仿真或者門及功能仿真;SmartModel庫用來模擬復雜的FPGA設計。

首先按如下步驟完成對XX的編譯:

(1)將ModelSim根目錄下的modelsim.ini文件的屬性設置為存檔;

(2)在ModelSim的命令窗口中輸入命令:“compxlib―s mti_se-arch all―l vhdl―w―lib all”;

(3)將ModelSim.ini文件的屬性重新設置為只讀。

環境建立好以后,首先對程序進行功能級仿真,驗證功能是否達到要求;功能仿真正確后再進行布局布線后仿真,根據布局布線仿真的情況再對程序進行分析,調整或者修改原先的設計,以滿足設計要求。

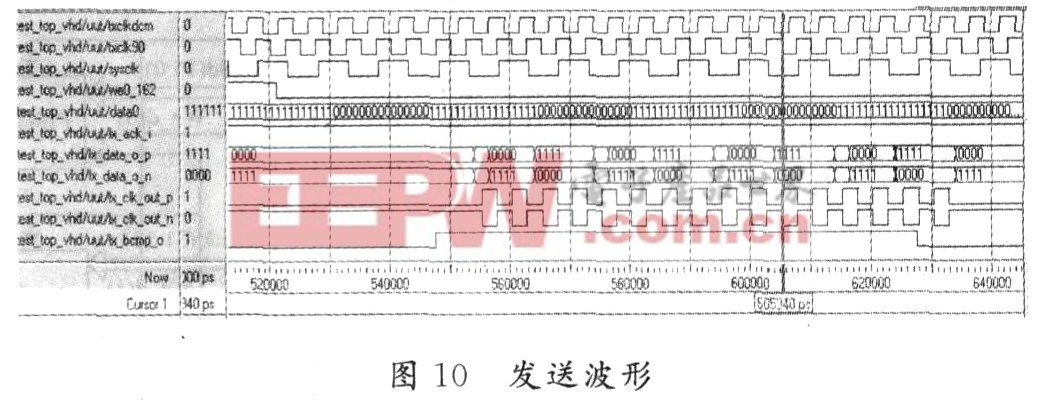

發送:此波形顯示將128位數據Data0轉換成鏈路口的傳送協議送出,如圖10所示。

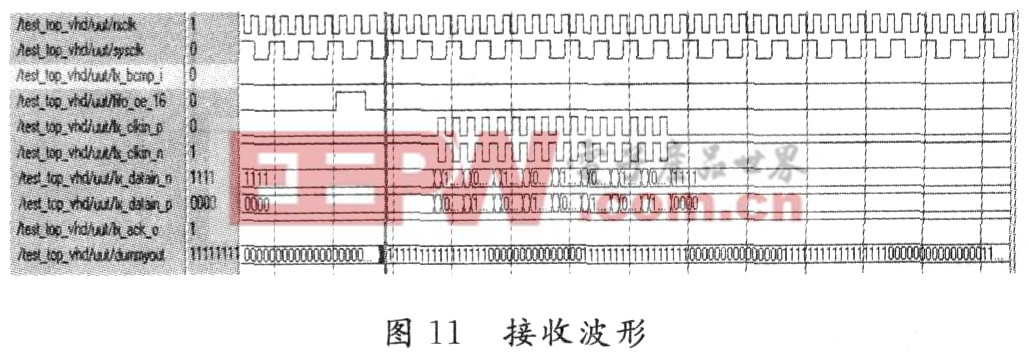

接收:此波形表示有TS201鏈路口接收到一組數據,當FIFO_oe(即FIFO讀信號)為高時將數據并行送出,如圖11所示。

結 語

本文介紹了一種利用VHDL語言在FPGA上實現鏈路口通信的方法,實現FPGA與ADSP TS201之間的高速鏈路口通信。設計最終能達到的接收鏈路時鐘頻率為500 MHz,發送鏈路時鐘頻率為400 MHz,充分發揮了鏈路口通信的速度優勢。也使得ADSPTS201通過具有此功能的FPGA與其他并行接口器件或設備進行高速通信成為可能。

評論