ADSP TS201鏈路口通信的FPGA實現

2 模塊建立與優化

ADSP TS201的鏈路口采用的是獨立的發送和接收通道,因此對應的FPGA也需要采用不同的接收電路和發送電路。

無論是接收還是發送均由兩部分組成:接收/發送緩沖和接收/發送模塊。接收模塊主要是用于接口和數據的拆包處理,發送模塊是用于數據接收和打包處理。接收/發送緩沖則是用來分別配合接收/發送模塊進行數據緩沖,并實現數據傳輸功能。

2.1 接收電路

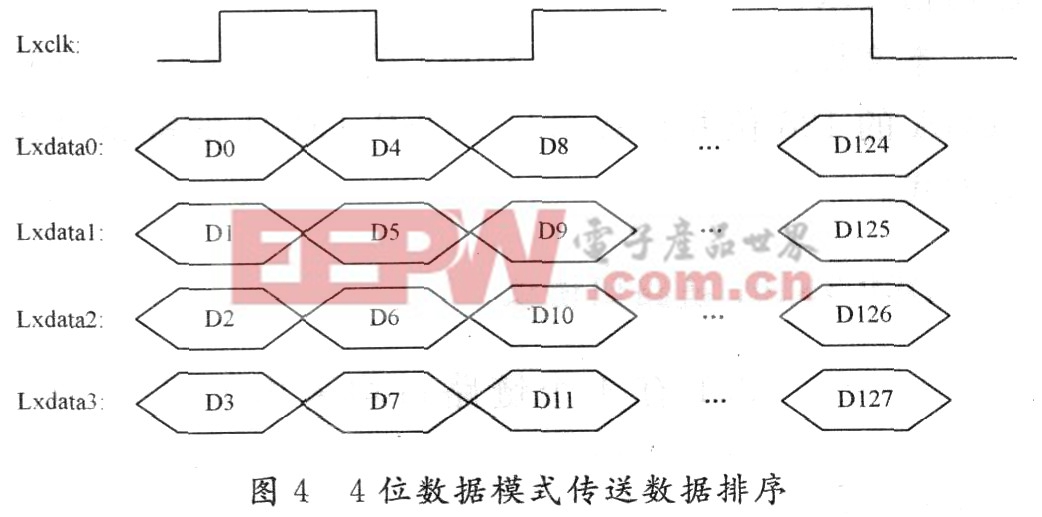

接收模塊:接收到由鏈路口4位數據總線送出的數據差分信號Lxdatap/n和控制差分信號Lxclk p/n以后不能直接拆包處理,需要將原來的差分信號轉換成完整信號、Lxdata和Lxclk,才可進入雙倍數據速率器(DDR)寄存,此寄存器由時鐘信號clkin(與Lxclk同頻率)控制。由于是4位數據總線同時串行傳送數據,其具體的數據排序如圖4所示。本文引用地址:http://www.104case.com/article/192061.htm

可見,每一路傳送的數據均不是連續的,且都按模4余數分配。為了方便數據并行送出,需要將數據進行拆包整理。每個clkin周期收到8位數據,將此按位號由大到小的順序整理,并放入mid(7:O)中。其間增加一級觸發器作為緩沖。

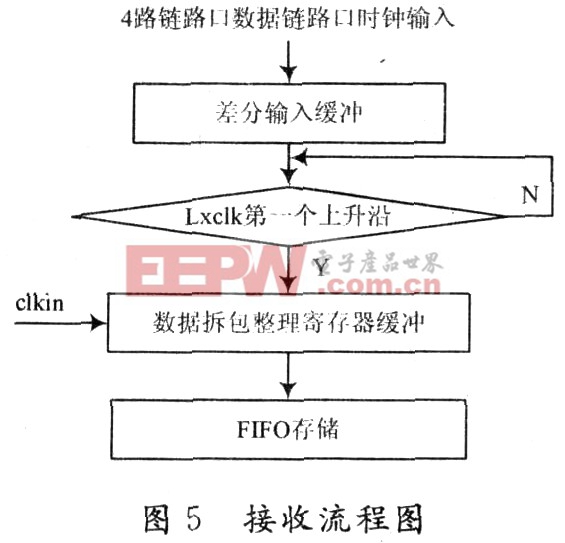

接收緩沖:此部分主要由狀態機和FIFO構成,其中狀態機主要控制FIFO寫命令的產生,由鏈路口時鐘Lxclk和時鐘信號clkin共同產生,即當Lxclk產生第一個上升沿時計數器開始計數從O~15,每次計數就會將相應的FIFO寫許可we d置為有效。將128位數據每8位為一組,分別送入16個8位F1FO中,由外部的FIFO_oe讀信號和sysclk時鐘信號控制128位數據并行讀出。即將FIFO_oe信號同時接到16個FIFO上,當FIFO_oe有效時,從16個FIFO中同時讀出數據。并根據FIFO存儲狀態發送Lxacko信號和fuiIflag信號,若FIF0不滿則將Lxacko信號置為1(高有效)允許發送端繼續通過鏈路口發送數據;否則Lxacko置為O。

其中,FIFO 8由Core generator直接生成,是異步8位先進先出存儲器。下面涉及的FIFO 16,FIFO 32均這樣生成。接收(Rx)流程圖如圖5所示。

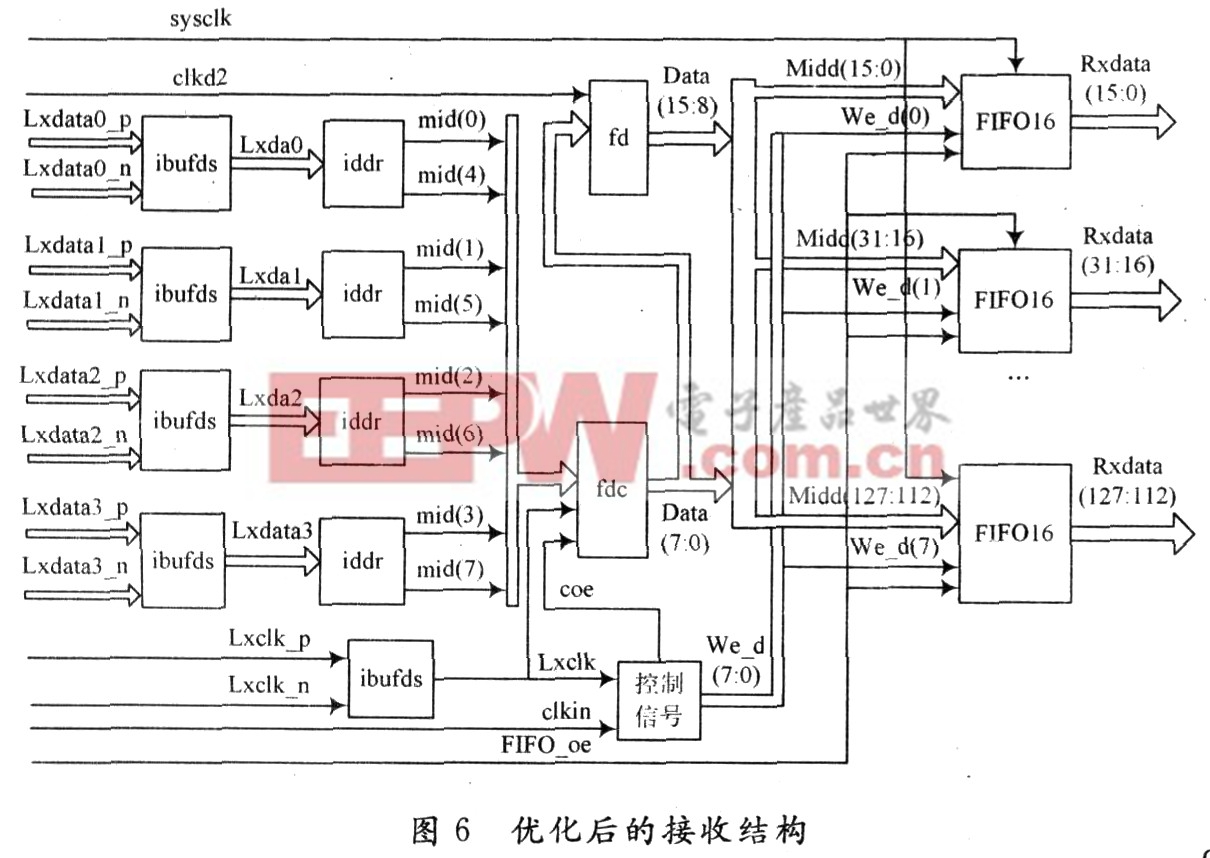

綜合后此電路的主時鐘Clkin頻率最快可達到368 MHz。由于一個FIFO 8就占用了一個18 Kb的嵌入式FIFO資源,而16個FIFO就占據了16個塊的資源,這不僅造成了資源的浪費,還增加了布局布線所需要的時間。因此,為了優化結構,增加一級寄存器,擴展數據的位數,使得數據在未進入FIFO前就已得到處理,由原來的8位數據mid連成16位數據Data,再送入16位的FIFO 16中。優化后,FIFO 16的使用率由原來的22%減少到11%,大大減少了線上延遲。綜合此電路的主時鐘clkin頻率最高可實現500 MHz。具體結構如圖6所示。

2.2 發送電路

評論