成功解決FPGA設計時序問題的三大要點

2.提供可視化的捕捉寄存器本文引用地址:http://www.104case.com/article/192059.htm

從導入時序報告文件開始, TimingDesigner軟件為關鍵信號延時創建變量,并在電子數據表中規劃和分配這些信號端口。變量過去是用來在時序圖中更新時鐘與數據關系。現在,可確定在FPGA器件內捕捉寄存器中的邊緣關系。

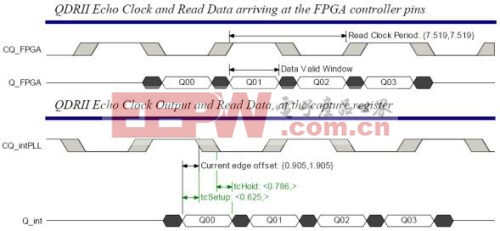

內部寄存器建立和保持是從時序報告和相關的約束中提取所需的時序。下一步,在時序圖表中添加另外兩個信號和偏移時序報告中的布線延時;在捕捉寄存器中添加數據和時鐘,然后建立和保持FPGA器件適用的約束。用時鐘邊緣和有效數據窗口邊緣的補償確定必要的相位偏移,來平衡設計中有效的數據窗口。

3.平衡有效數據窗口

我們可以使用下列公式來確定PLL時鐘信號產生的相位偏移:

1、從設計的實際有效數據窗口減少FPGA裝置I/O部分的最小有效數據窗口,然后結果除于2,實際結果為這2個有效數據窗口的差額(DlyDVW)。(參考圖3)

DlyDVW = (DVWdata - DVWdev) / 2

2、I/O寄存器數據建立時間加上DlyDVW值,就確定了相對時鐘邊緣的有效數據窗口(DlyRelSU)。

DlyRelSU = DlyDVW + IOEsu

3、最后,從相對建立時間(上面第2步得到的數值),減去時鐘信號與捕捉寄存器的有效數據窗口(從時序圖測量)之間的補償。

Clk_offset = DlyRelSU - EdgeOffset

利用上述公式,我們可以確定FPGA開發系統中PLL的相位偏移量,并執行到下一步的布局和布線。

4.驗證結果

再次導入做過以上修改的布線后時序文件,TimingDesigner軟件會自動更新需要的數值,并更正及重新定位I/O單元的時鐘信號CQ_intPLL。如圖6所示。依靠改變PLL,確切的平衡建立和保持空余將是不可能的。對于這些情況下,應該在FPGA裝置的PLL中獲取平衡增量以解決這個問題。

圖6:在改變時鐘和平衡建立及保持空余后,獲取數據分析的時序圖表。

本文小結

高速設計往往有嚴格的規范和嚴謹的發布時間表,所以需要一個交互式的時序規劃和分析工具,來獲得快速和完整的時序空余,以分析并解決可能影響到最終設計成功的因素。本文說明了如何利用TimingDesigner軟件對FPGA設計流程進行準確地捕捉和交換時序信息,以幫助在整個設計過程中管理時序空余,并提供可視化的界面驗證設計,并預測設計性能。今天的FPGA器件產品都帶有多功能的時鐘配置和豐富的I/O資源,并且帶有高數據傳輸能力,TimingDesigner軟件為高速存儲器如DDR QDR SRAM提供精確的關鍵路徑時序分析功能。

評論