基于FPGA的多功能信號源生成系統設計與實現

3.1 控制參數接口轉換模塊

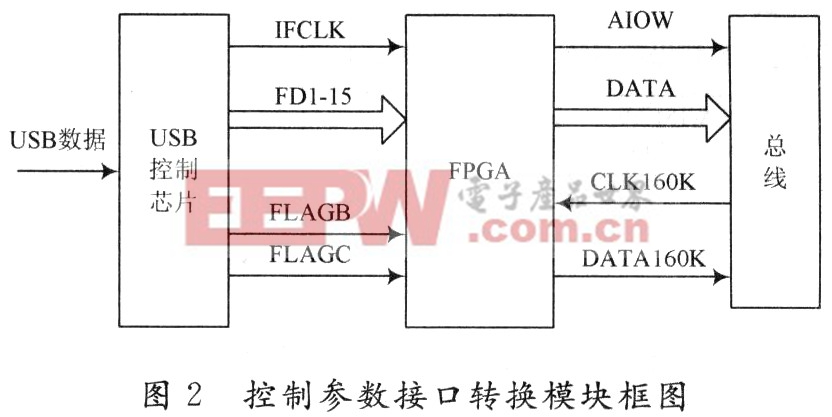

控制參數接口轉換模塊完成從USB接口中收到的數據接收,并將接收數據轉換為總線數據送入背板總線。控制參數接口轉換模塊主要包括兩個部分:USB控制芯片和1片FPGA,如圖2所示。在這個模塊內完成數據包的獲取和拆分兩個操作。數據包的獲取就是USB控制芯片將USB傳輸線中的1位數據轉換為16位的FD信號,送到FPGA中。FPGA再將接收到的數據按照數據包拆分協議分成16位控制參數信號DATA與160 kHz的數字基帶信號DATAl60K送到背板總線,同時通過總線進行傳輸的還有兩個時鐘信號AIOW和CLKl60K。其中AIOW是與控制參數信號DATA相匹配的時鐘,是由FPGA送入總線中的,而CLKl60K是與數字基帶信號DATAl60K相匹配的時鐘,是由信號生成器通過總線送入FPGA中的。數據包的拆分主要由1片Spartan3 FPGA(XC3S200)來實現。本文引用地址:http://www.104case.com/article/192039.htm

3.2 信號生成模塊

信號生成模塊采取FPGA和高速D/A相結合的方法,在FPGA內部產生高速采樣數據。采樣數據送人高速D/A中還原出信號。在該系統中,FPGA芯片選用Xilinx公司Virtex-4系列的XC4VLXl00,而高速D/A選用AD公司的AD9736。如圖1所示,信號生成模塊包括2塊信號生成電路板,每塊電路板上有2塊FPGA和4塊高速D/A,每塊FPGA與2個D/A相連,即1個FPGA內部需要同時產生2路信號采樣數據,整個系統能產生8路信號。

FPGA的工作時鐘是射頻模塊生成的時鐘在高速D/A內完成二分頻后送給FPGA的。由于每塊FPGA與2個D/A相連,因此它也有2個時鐘輸入。為了保持時鐘與數據的同源特性,在FPGA內部電路設計中采取了并行設計的方法,即送給高速D/A的高速采樣數據與其匹配的時鐘完全是由其送入的時鐘來產生的,而與另一個D/A送入的時鐘完全無關,保持了各路信號之間的獨立性。同時,射頻模塊可以產生相參和非相參的時鐘,從而使得系統能產生相參和非相參信號。另外,送入D/A的時鐘也可由外部送入,大大增加了系統的靈活性。

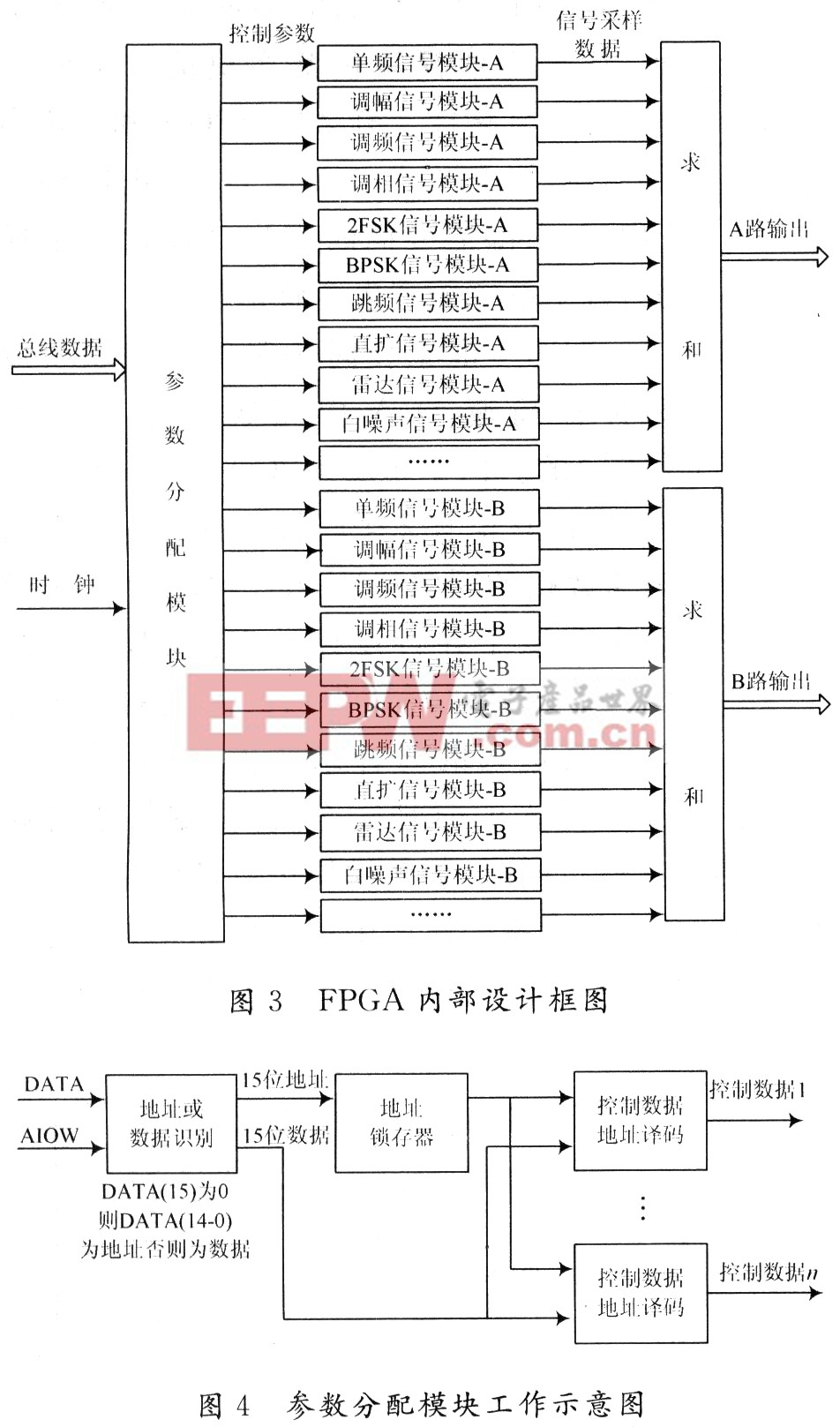

FPGA內部采取了模塊化設計方法,包括參數分配模塊、各種信號采樣數據生成模塊和信號求各種信號采樣數據生成模塊和信號求和模塊,其設計框圖如圖3所示。參數分配模塊主要將總線接收到的各路信號中控制參數信號DATA分配到各信號采樣數據生成模塊中,其內部控制示意圖如圖4所示。參數分配模塊在時鐘AIOW的上升沿時刻,按照控制參數信號DATA的高位情況,識別DATA低15位為地址還是數據,如果為地址則送往地址鎖存器鎖存;如果為數據則送往地址譯碼器,由地址譯碼器根據譯碼協議判定數據為特定信號采樣數據生成模塊的特定控制參數。信號采樣數據生成模塊則根據所分配的參數生成所需信號采樣數據送往求和模塊。為了減少信號經過求和模塊帶來信號能量的損失,設計中不是采用傳統截取高位輸出的方式,而是采取了截取低位輸出的方式,這種方式保證了求和器在沒有溢出的情況下,能維持系統指定參數的信號輸出,而不損失信號能量。為了防止求和器溢出,產生失真信號,在綜合控制器中做相應處理,使得控制人員輸入的控制參數在合適的范圍之內。

評論