基于FPGA的多功能信號源生成系統設計與實現

摘 要:為了滿足科研與實驗需要,提出并實現了一種以FPGA和高速D/A為核心,其結構簡單,控制靈活,信號質量高的多功能信號源生成系統。該信號源生成系統能夠實時產生中心頻率在30~130 MHz的各種雷達、通信、導航和白噪聲等信號,且產生的各種信號頻率、幅度、相位和其他參數均可控。信號源作為基帶信號單元配以混頻模塊,可實現在任意頻段的信號。另外,該信號源還可以作為一個通用平臺,通過FPGA內部程序的更新來實現其他復雜信號。

關鍵詞:FPGA;信號源;硬件設計;AD9736

產品級的信號源往往滿足不了科研和實驗的需要,尤其在復雜電磁環境的研究和實驗中,需要的信號樣式多種多樣,而且根據場景的不同,需要信號樣式、個數都發生了改變。

現場可編程邏輯陣列器件(FPGA)繼承了ASIC中大規模、高集成度、高可靠性的優點,克服了普通ASIC設計周期長,投資大,靈活性差的缺點,逐步成為復雜數字硬件電路設計的理想首選。為了能滿足科研與實驗的需要,產生一系列需要的信號,設計了一種以FPGA和高速D/A為核心.能產生中心頻率在30~130 MHz的、各種參數均可調的雷達、通信、導航和噪聲信號的多功能信號源生成系統。

1 系統硬件結構

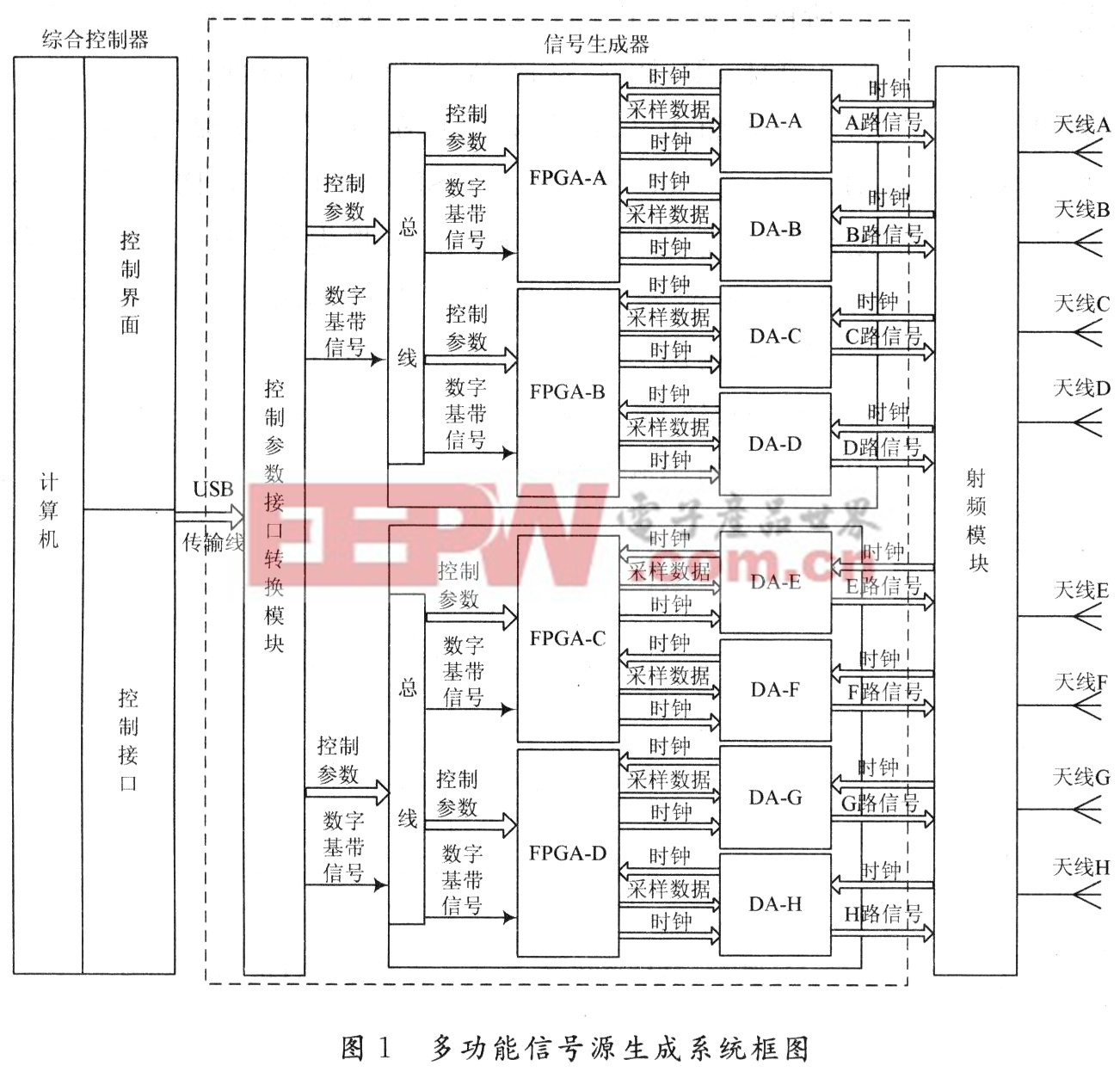

多功能信號源生成系統在綜合控制器的控制下產生一個或多個中心頻率在30~130 MHz的雷達、通信、導航、噪聲等信號,輸出電平一60~o dBm.步進值為0.06 dB。系統主要由綜合控制器、信號生成器、射頻模塊和天線4個部分構成,如圖1所示。綜合控制器實現對系統的整體控制,包括信號路數及各路信號參數。信號生成器主要包括控制參數接口轉換模塊和信號生成模塊兩個部分。射頻模塊主要完成兩項功能,即650 MHz時鐘的生成和對輸入的中頻信號變頻,最后經天線輸出信號。

2 綜合控制器

綜合控制器為一臺工控計算機,主要完成控制參數的輸入和數字基帶信號生成。控制人員通過綜合控制器控制界面將控制參數輸入,這些控制參數經過計算機uSB接口輸入到信號生成器,實現對信號生成器的控制。數字基帶信號是一定速率的二進制碼流,在該系統中綜合控制器完成將BMP圖片轉換成一定速率的二進制數據,并通過USB接口輸人到信號生成器中,作為系統的數字基帶信號。綜合控制器在工作時,負責向信號生成器注入控制參數,如信號路數和各路信號參數(信號樣式、工作頻率、功率輸出、調制指數、延遲時間、跳頻速率、脈寬、脈沖周期等),當控制參數輸入完畢后,綜合控制器開始利用USB接口傳輸由BMP圖片轉換的二進制數據。系統在工作過程中可實時更改控制參數,并根據指令進行刷新,此時數字基帶信號傳輸將暫停,等待更新完畢后繼續輸出。

3 信號生成器

信號生成器由兩部分構成,即控制參數接口轉換模塊和信號生成模塊。控制參數接口轉換模塊完成將綜合控制器通過USB傳輸線傳輸的控制參數和數字基帶信號轉換為總線數據送入總線中,由信號生成模塊產生特定控制參數的信號。

評論