基于CPLD的鍵盤控制器設計

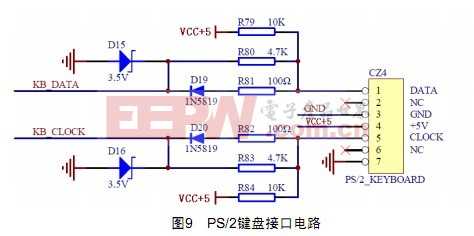

通過這樣的處理既滿足設計的需要,又起到對器件保護的作用。EN是掃描電路的使能輸入端,高電平有效。它通過去抖動后的列回復線相與得到。當有按鍵按下時,相應的列線將被置低。相與的結果為低,這使掃描電路停止掃描,等待控制器對掃描結果進行處理,得到相應的鍵值送入鍵值鎖存器,等待單片機讀取。這樣做的好處是可防止控制器漏掉按鍵的讀取。根據調試得知,鍵盤掃描時鐘信號最好是去抖電路時鐘的四分頻以上。所以CLK是通過對去抖電路的時鐘進行分頻得到的。圖3給出實現掃描電路的具體原理圖。本文引用地址:http://www.104case.com/article/192036.htm

(2)該設計中采用4×4的鍵盤,有16個按鍵狀態,再加上一個沒有鍵按下的狀態共有17個狀態,而4位二進制數只能表示16個狀態。為了解決這個問題,將R4和L4或非后再與計數器產生的中斷信號相或,產生一個單片機中斷。當按下最后一個鍵時,鍵盤控制器便產生1個中斷,讓單片機來讀取這個按鍵值0000(在沒有鍵按下時也是這個狀態),從而區分了無按鍵狀態和最后一個按鍵按下的狀態。這樣在編碼的時候只需考慮前15個鍵的狀態信息。最終可用4位二進制數表示所有按鍵狀態。圖4給出實現編碼器的具體原理圖。

(3)鍵盤去抖動電路主要由2個DQ觸發器和1個基本RS觸發器組成。當有鍵按下時,理想情況下相應的列線應該是一直保持低電平。

但是實際應用中不可避免地產生抖動,此時列回復線將發生長短不等的高電平跳躍現象。鍵盤去抖電路就是去除這樣抖動的高電平對按鍵鍵值檢測帶來的干擾。為了消除這樣的干擾,去抖電路采用兩級延時策略。

只要抖動的高電平持續時間在去抖電路的2個時鐘周期之內,這種抖動是不會被引進編碼電路的。鍵盤去抖電路的具體原理圖實現如圖5所示。

3 仿真實驗及分析

3.1 掃描電路的輸出仿真波形

鍵盤控制器掃描電路的輸出仿真波形如圖6所示。在圖6中掃描電路的輸出端依次循環輸出低電平來掃描鍵盤的每一行,圖中L1~L4是沒有加三態門的掃描器輸出,其作為編碼電路的輸入,R1~R4是加三態門的輸出波形,從圖3中可以看出當L1~L4的輸出是高電平時,R1~R4的輸出狀態是高阻。

評論