基于CPLD的全幀型CCD圖像傳感器驅(qū)動系統(tǒng)設計

首先由CLK時鐘產(chǎn)生模6計數(shù)器sell、模4764計數(shù)器sel2和模6計數(shù)器sel3。由于sell和sel2相互作用,當滿足ENA=1且sel2≥683(由圖3可得出)時,則相應可產(chǎn)生C1,C2,c3信號值,否則全部賦為0。而A1,A2,A3,A4則是在SEL2和SEL3的共同作用下,將主時鐘信號進行分頻后作為時鐘,在滿足圖6中所羅列的條件后,根據(jù)SEL2值的變化即可給出A1~A4的值。

采用這種模塊化的設計,其光積分時間、行轉(zhuǎn)移頻率和像轉(zhuǎn)移頻率、行轉(zhuǎn)移數(shù)和每行像素轉(zhuǎn)移數(shù)均可調(diào)整,程序的移植性較好,可適用于不同的需要,而且也方便調(diào)試。

3 實驗結(jié)果分析

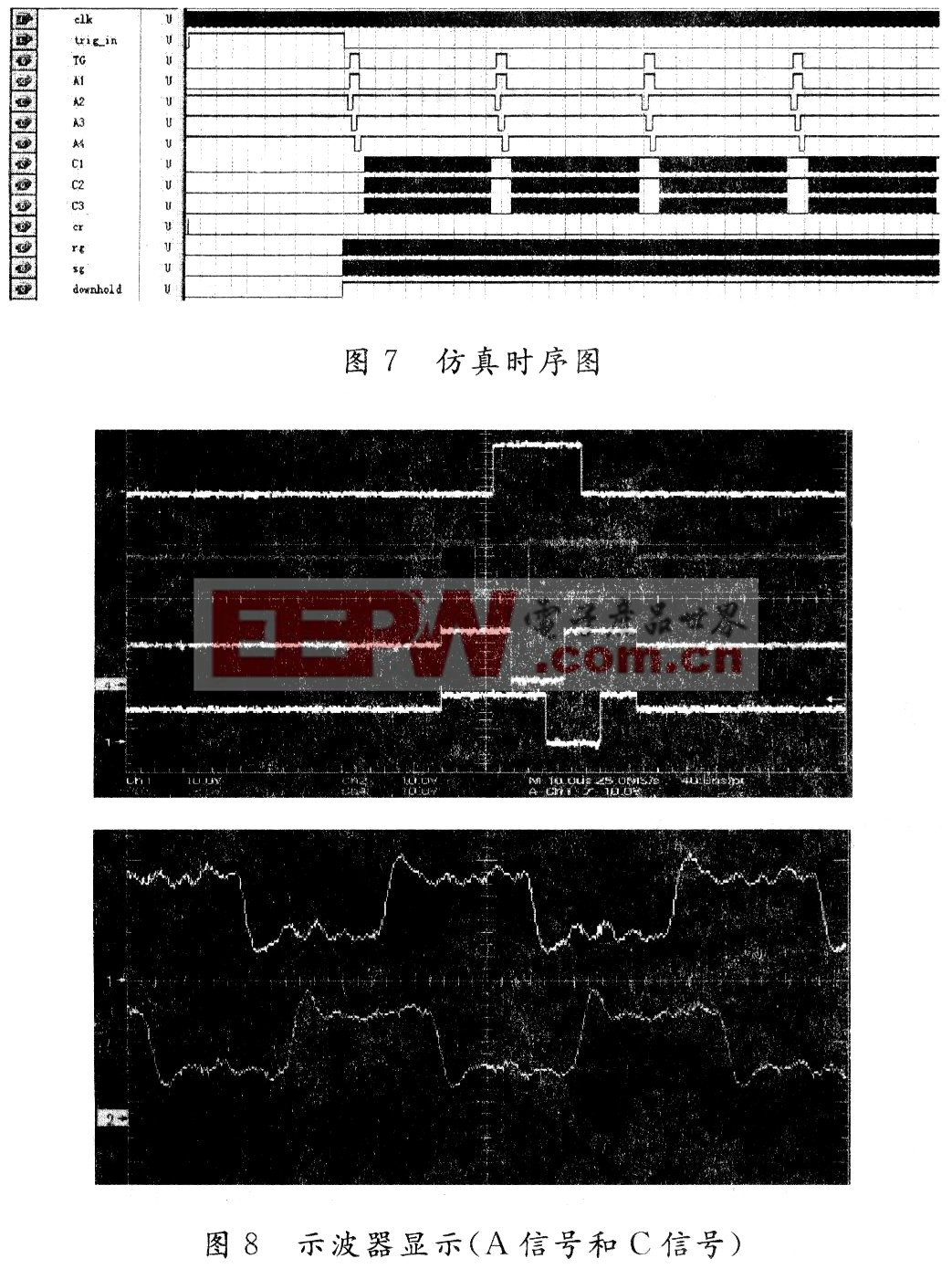

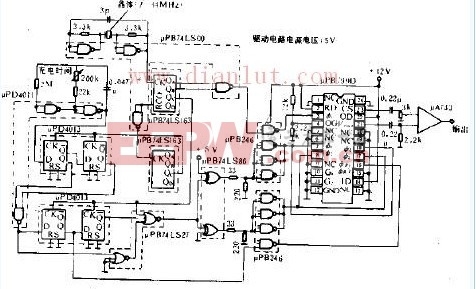

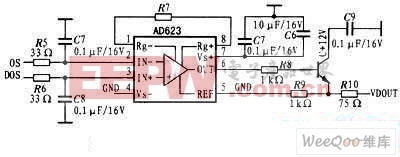

對程序進行系統(tǒng)仿真后的時序圖如圖7所示。可看出該時序符合CCD芯片的datasheet要求。將編譯好的程序下載到CPLD中,通過示波器可以得到所需的驅(qū)動信號,如圖8所示。

在實驗中發(fā)現(xiàn),雖然軟件仿真中各個驅(qū)動信號能夠嚴格符合CcD4052M要求的時序關系,但是實際輸出到CCD信號的驅(qū)動信號卻仍然有不同程度的延時。這主要是由兩方面的原因引起的。首先,由于在設計初期采用的是集成開發(fā)環(huán)境下行為級的仿真功能,仿真過程不包括延時信息,只為驗證代碼行為的正確性,可以做到與器件無關,所以CPLD的輸出會與仿真結(jié)果有所差異;其次,CCD驅(qū)動信號由CPLD產(chǎn)生后,需要經(jīng)過后續(xù)的模擬驅(qū)動電路,由于電子器件本身的特性和差異,造成了抵達CCD管腳的驅(qū)動信號具有不同的延時。其中,第一種誤差可以通過進行集成開發(fā)環(huán)境下的時序級仿真解決。這種仿真為設計的每一個底層器件加入了延時信息,可以模擬到比較接近實際電路的行為。第二種誤差因電子器件本身造成的,存在個體性差異,無法進行精確的計算。解決方法是在電路設計中加入延時芯片,通過實際測量,設定不同延時芯片的延時,校正各個驅(qū)動信號間的誤差。

4 結(jié) 語

該CCD驅(qū)動系統(tǒng)采用CPLD芯片進行設計,具有性能好,功耗低,體積小的特點。該驅(qū)動電路的研制結(jié)果表明,采用CPLD專用集成芯片進行系統(tǒng)設計有它自身的優(yōu)點,可以簡化設計,并且調(diào)試簡單,可擴展性也比較強。

評論