基于CPLD的全幀型CCD圖像傳感器驅動系統設計

光積分結束后進人第三階段,即幀轉移階段,而幀轉移又可以看成是垂直行轉移和水平像素轉移交替進行的,它們之間的轉換通過SSC電平的高低轉換實現。

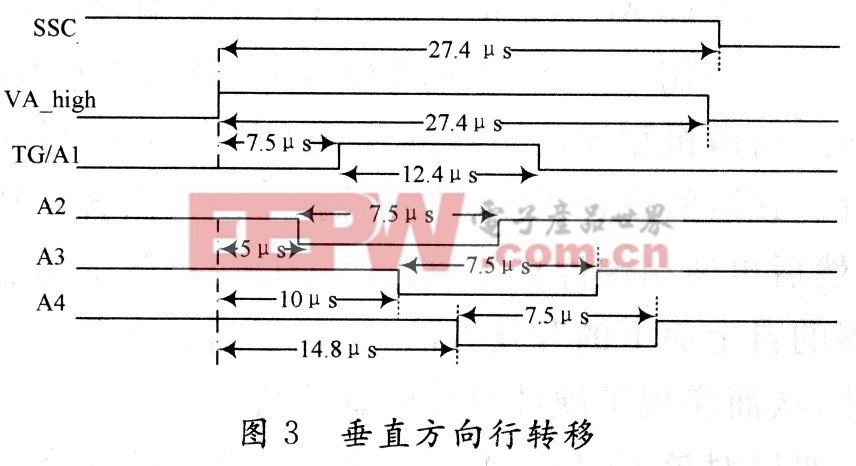

SSC上升沿的到來標志著一次水平像素轉移的結束和一次垂直行轉移的開始,CCD像素垂直方向的行轉移是由A1,A2,A3,A4等時鐘及像素傳輸門TG時鐘來完成的,其頻率都為50 kHz,且四相A時鐘信號要滿足嚴格的交迭原理。在SSC保持高電平時,如圖3所示,光敏區里已經生成的電荷包在四相A時鐘信號的驅動下逐行地向上和向下轉移到輸出寄存器。本文引用地址:http://www.104case.com/article/192035.htm

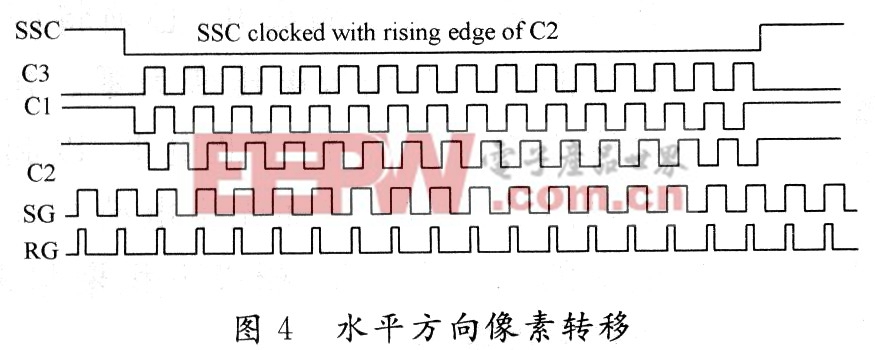

SSC下降沿到來時,標志著一次垂直行轉移的結束和一次水平像素轉移的開始,CCD像素水平方向像素的轉移是由C1,C2,c3等時鐘來完成的,信號頻率都為25 MHz。其轉移原理與垂直行轉移原理一樣,三相C時鐘信號亦要嚴格滿足三相交迭原理。如圖4所示,輸出寄存器就是在三相C時鐘信號的驅動下將這一行逐個像素向輸出放大器轉移的。

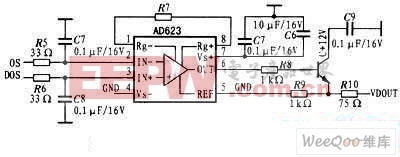

RG(Reset Gate)是通過復位管對輸出放大器的浮置擴散電容(Floating Diffusion Capacitante,FD)進行復位的信號,其中FD可以將接收到的電荷包轉換為電壓信號。復位后FD可以接收下一個電荷包。SG(Summing Gate)是在輸出柵OG之前的最后一個柵,SG信號和RG信號的相位與C3信號的相位相同。一行電荷包經過輸出放大器的轉換和放大后,以電壓信號的形式從CCD輸出。接下來再進行下一行的垂直行轉移和水平像素轉移輸出,直到將光敏面上的所有5 356行電荷包輸出完畢為止。由此可見,整個一幀圖像是在A時鐘信號和C時鐘信號的交替驅動下從CCD芯片的輸出放大器輸出而完成幀轉移的。

2 驅動系統設計

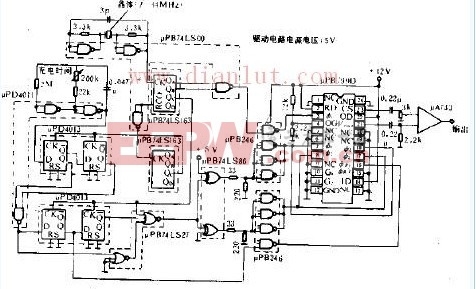

隨著大規模可編程器件的迅速發展和廣泛使用,傳統的通過TTL標準電路構成的積木式電路系統已經慢慢被淘汰。目前較為流行的CCD驅動電路設計方案一般有兩種:一是用FPGA或者是CPLD產生CCD的時序驅動信號,以及用模擬電路(功率放大晶體管和電位器)實現對CCD的直流電平驅動信號;另一種則是用專用的CCD驅動芯片,實現對CCD的驅動。前者要求開發者對硬件描述語言熟悉,而且實現靈活,集成度高,方便功能的升級和擴展;后者則只需對寄存器進行設置,編程較為簡單,但是可擴展性稍差。在此,采用Altera公司EPM7160SIC 84-10型可編程邏輯器件(CPLD),使用Altera公司的QuartusⅡ集成開發環境,并通過與微機相連的下載線實現CPLD的燒寫和在線編程。頂層的設計采用原理圖輸入,設計出各個功能模塊,然后再使用硬件描述語言(VHDL)對各個功能模塊編程的自上而下的開發方法,實現了高層次復雜邏輯的設計,從而實現了硬件設計的軟件化。

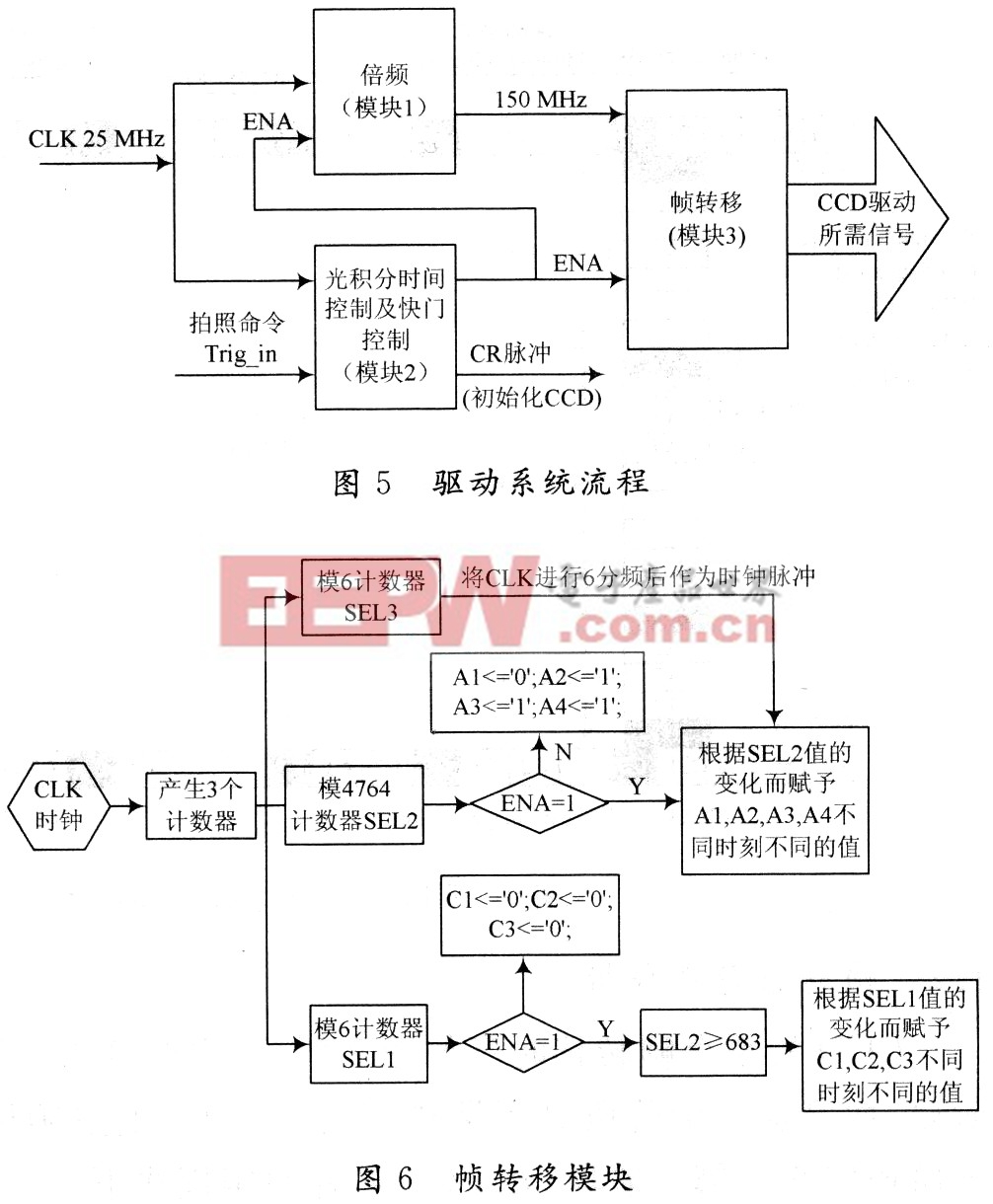

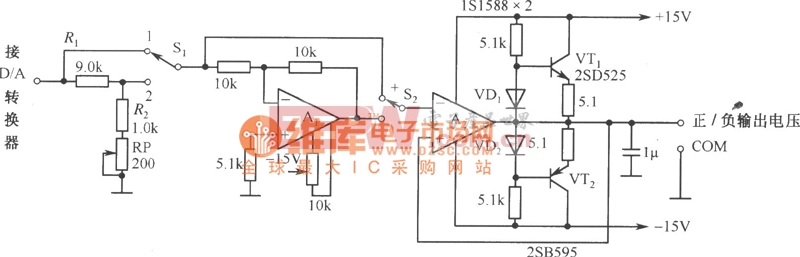

通過對該CCD芯片的了解,將頂層設計分為3個功能模塊,分別為倍頻模塊(模塊1)、光積分時間控制及快門控制模塊(模塊2)、幀轉移模塊(模塊3),各功能模塊的關系如圖5所示。模塊1為倍頻模塊,通過調用該模塊,可產生幀轉移所需的頻率脈沖信號。由于CPLD芯片一般不帶有PLL模塊,故可采用延時加異或的方式來實現倍頻。不過目前較新的CPLD,如Lattice的MachXo系列器件則可直接調用PLL,此處不再贅述。模塊2為光積分時間及快門控制,通過拍照指令產生CR脈沖信號,對CCD進行初始化,并生成一個在光積分期問保持高電平的使能信號ENA。將ENA分別發送至模塊1和模塊3。CR信號和ENA可通過對按鍵信號Trig―in的延遲處理來實現,也較為簡單。該設計中最關鍵的是幀轉移模塊。其原理主要是利用3個計數器進行相互嵌套,從而產生所需的驅動信號,其簡易流程如圖6所示。

評論