使用 FPGA 控制 VGA 顯示

而與我們電腦相關(guān)的地方,就是目前的顯示器大都是采用了 RGB 顏色標(biāo)準(zhǔn),這就是為什么它對(duì)我們來說這么重要了。

在顯示器上,是通過電子槍打在屏幕的紅、綠、藍(lán)三色發(fā)光極上來產(chǎn)生色彩的,目前的電腦一般都能顯示 32 位顏色,約有一百萬種以上的顏色。如果說它所顯示的顏色 還不能完全吻合自然界中的某種色彩的話,那已經(jīng)幾乎是我們?nèi)庋鬯荒芊洲q出來的了。

而 RhicSP2200 開發(fā)板系統(tǒng)中每一個(gè)色 彩都是使 用 2bit 來 表示的,因 此可見 RhicSP2200 系統(tǒng)可以出現(xiàn)64 種不同的顏 色。其他色彩的使用請(qǐng)?jiān)趯?shí)際工作中更多的加以體會(huì)。

顯示

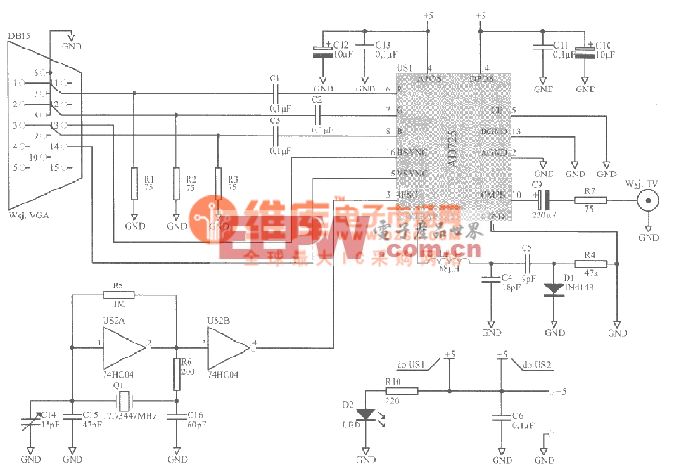

通過以上的講述,已經(jīng)可以在計(jì)算機(jī)顯示器上顯示一個(gè)有顏色的區(qū)域了,在這個(gè)小節(jié)中我們?cè)倥e一個(gè)簡(jiǎn)單的例子,在顯示器中顯示兩個(gè)鑲嵌的正方形,字符等顯示與其類似,可以參考瑞芯科技其他設(shè)計(jì)示例。 例如我們可以在 xpos 與 ypos 的某一區(qū)間給 RGB 信號(hào)賦不同的值將得到如圖2 所示的顯示效果。

例子 1:使用 50MHz 時(shí)鐘頻率產(chǎn)生的 VGA 同步脈沖以及視頻有效信號(hào)

module sync_gen_50m(

rst_n,// synthesis attribute clock_buffer of rst_n is ibufg;

clk,

hsync,

vsync,

valid,

x_cnt,

y_cnt

);

input rst_n ;

input clk ;

output hsync ;

output vsync ;

output valid ;

output [9:0] x_cnt ;

output [9:0] y_cnt ;

reg hsync ;

reg vsync ;

reg valid ;

reg [9:0] x_cnt ;

reg [9:0] y_cnt ;

always @ ( posedge clk or negedge rst_n )

if ( !rst_n )

x_cnt = 10'd0;

else if ( x_cnt == 10'd1000 )

x_cnt = 10'd0;

else

x_cnt = x_cnt + 1'b1;

always @ ( posedge clk or negedge rst_n )

if ( !rst_n )

y_cnt = 10'd0;

else if ( y_cnt == 10'd665 )

y_cnt = 10'd0;

else if ( x_cnt == 10'd1000 )

y_cnt = y_cnt + 1'b1;

always @ ( posedge clk or negedge rst_n )

if ( !rst_n )

begin

hsync = 1'b0;

vsync = 1'b0;

end

else

begin

hsync = x_cnt = 10'd50;

vsync = y_cnt = 10'd6;

end

always @ ( posedge clk or negedge rst_n )

if ( !rst_n )

valid = 1'b0;

else

valid = ( ( x_cnt > 10'd180 ) ( x_cnt 10'd980)

( y_cnt > 10'd35) ( y_cnt 10'd635) );

endmodule

評(píng)論