基于FPGA技術實現與PC串行通信

控制模塊本文引用地址:http://www.104case.com/article/192024.htm

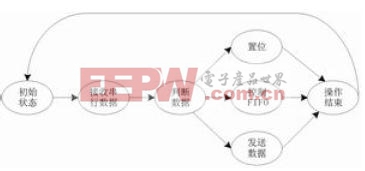

主要實現的功能是:判斷從PC接收的數據,根據預先設計的邏輯進行相應的狀態轉換。例如:給端口預置一個狀態;送開始發送的標志位,送準備發送的數據;給DDS送配置信號,控制FIFO的讀寫。程序中狀態機設計如圖3所示。

圖3 狀態機變換

設計中需要注意的問題

波特率的選擇對于串口通信是很重要的,波特率不應太大,這樣數據才會更穩定。整個發送接收過程中起始位的判別和發送是數據傳輸的前提。為了避免誤碼的產生,在FPGA設計中的串行輸入和輸出端口都應該加上一個數據鎖存器。

仿真結果

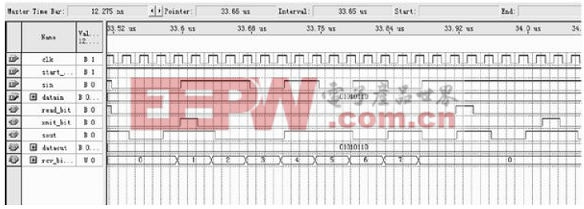

基本的發送接收如圖4所示,clk是時鐘信號(57600 bit/s);start_xmit是開始發送標志位;sin是串行輸入;datain是并行輸出;read_bit是接收結束標志位;xmit_bit是發送結束標志位;sout是串行輸出;dataout是并行輸出;rcv_bit 是接收位數寄存器。發送接收模塊主要完成把從sin端口接收的串行數據變為并行數據送給dataout;把并行數據datain變成串行數據通過sout端口串行發送。

圖4 發送接收過程

接收:判斷接收的串行數據sin是否是連續的兩個0,如果是則進入接收過程;每兩個時鐘周期接收1個比特的數據,依次接收到01101010,如果接收到停 止位表明這個接收過程結束read_bit=1。根據串行通信協議,數據是按照先低位,后高位的順序發送的,所以實際接收的是01010110。發送:待發送的并行數據為01010110,當start_xmit=1發送有效,進入發送過程;首先發送兩個起始位0,保證長度為兩個時鐘周期,然后依次發送01101010,每兩個時鐘周期發送1比特,最后發送停止位,發送過程結束xmit_bit為1。

發送控制字

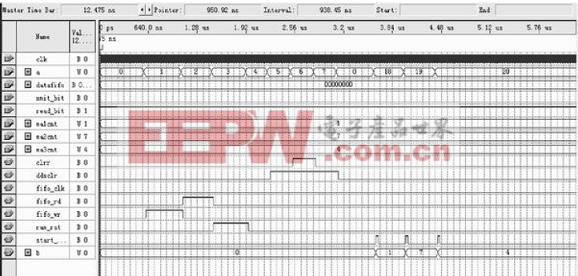

圖5中clk是時鐘信號;a是PC發來的16進制的控制字,也就是圖4中的并行輸出dataout; ma1cnt、ma2cnt、ma3cnt是三個寄存器;clrr是系統清零信號;ddsclr是DDS配置信號;fifo_clk,fifo_rd,fifo_wr,ram_rst是FIFO的時鐘、讀、寫、清零信號;start_xmit是發送開始標志位;b是準備發送的數據。當接收a為1時,fifo_wr置1;當a為18時,把ma1cnt的值送到b。其他的操作類似,主要是端口的置位,FIFO讀寫狀態的控制。

圖5 發送控制字過程

從FIFO中讀寫數據

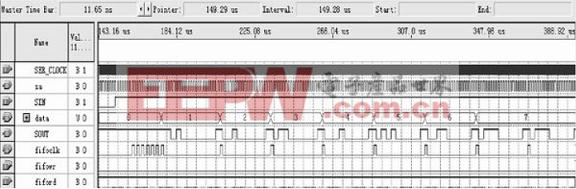

圖6中SER_CLOCK是系統時鐘3.6864MHz,sa是分頻后的頻率57600bit/s;SIN是串行輸入;data是準備輸出的數據;SOUT是串行輸出;fifoclk、fifowr、fiford是FIFO的讀時鐘、寫、讀使能。讀過程:讀使能有效,先產生6個讀時鐘,但是不往SOUT發送數據,因為FIFO的前6個周期不是有效數據。然后產生一個讀時鐘,將FIFO的數據送到data,按照通信協議通過SOUT發送出去,發送結束再產生一個讀時鐘,讀取FIFO的數據,進行下一次串行輸出。

圖6 從FIFO讀數據的過程

結語

隨著可編程器件的不斷發展和廣泛應用,FPGA與外圍設備的通信也越來越多。本文介紹的串行通信的實現具有可復制性,只需改變系統時鐘頻率和控制模塊就可以在其他場合下使用。

評論