VGA時序發生器設計

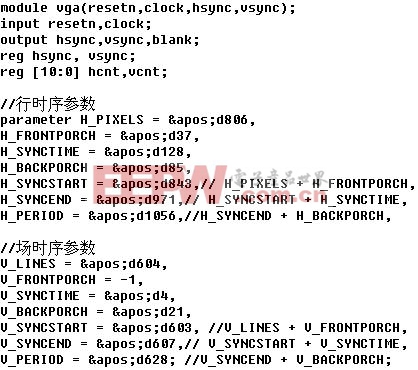

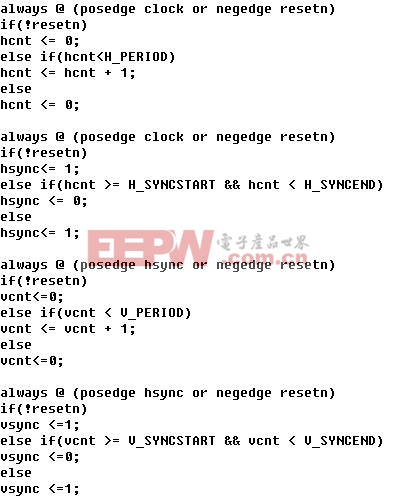

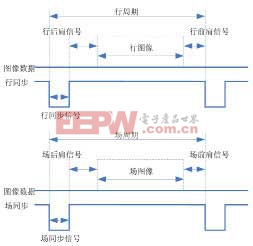

VGA標準時序參考圖如圖7所示,并用VERILOGHDL設計For VESA 800*600 @ 60Hz:VGA時序的源代碼:

圖7 VGA標準時序參考圖

系統分析

經過反復測試,系統能夠將采集端數據實時傳送到顯示器上,具體性能指標如下:

視頻輸出:VGA視頻輸出

視頻顯示DA轉換精度: 10bit

圖像輸出標準: SVGA(75Hz, 800×600)

顯示分辨率: 10bit

結語

該VGA視頻顯示系統不但可以穩定地采集圖像數據,而且可以實時將數據傳輸到CRT顯示器,便于以后人工綜合分析、處理。它特別適用于大型商場等顯示端,可以說是一個理想的解決方案。

評論