基于CPLD的VGA視頻顯示系統的設計

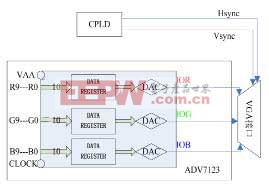

視頻DAC模塊

ADV7123是一個三路10位輸入的高速視頻DAC,具有330MHz的最大采樣速度,與多種高精度的顯示系統兼容,包括RS-343A和RS-170,可以廣泛應用于如HDTV、數字視頻系統(1600*1200 @100Hz)、高分辨率的彩色圖片圖像處理、視頻信號再現等,因此能夠滿足多方面應用需求。視頻DAC(ADV7123)工作原理如圖3所示。

圖3 ADV7123工作原理

CPLD提供Hsync(行)、Vsync(場)同步信號,直接接入15針的VGA顯示接口連接器。在點時鐘脈沖pixel clock的作用下將3路10位的RGB信號送入數據寄存器,而后送到3個DAC模塊,復合消隱信號和復合同步信號加到紅、綠、藍模擬信號送到輸出端。

系統軟件設計

系統軟件設計是本文的重點,主要包括三部分內容:SRAM讀寫狀態機的設計、CPLD與SRAM的緩沖模塊通信以及VGA時序設計。

SRAM讀寫狀態機的設計

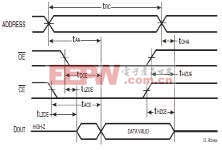

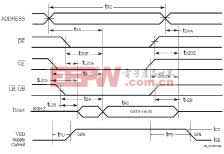

以6416為核心的圖象處理機通過外部存儲器接口向外傳送數據,連接到后端的顯示系統;但SRAM需要嚴格的通信時序確保數據的完整性,此處在CPLD內部通過狀態機構造SRAM的讀時序和寫時序,確保了6416能夠和SRAM正常通信,也確保緩沖模塊的正常運行。讀寫SRAM的時序圖如圖4和圖5所示。

圖4 讀周期時序圖

圖5 寫周期時序圖

當從SRAM中讀取數據時:首先使能片選;UB、LB時鐘處于有效狀態;WE為高,時鐘處于無效狀態;主要由OE的時序來控制使其符合讀時序圖,才能正確地讀出存儲器中的數據。在向SRAM中寫入數據時,同樣首先使能片選;UB、LB時鐘處于有效狀態;OE為高,時鐘處于無效狀態;主要由WE的時序來控制使之符合寫時序圖,才能向存儲器正確寫入數據。

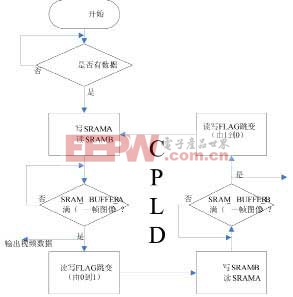

CPLD與SRAM組成的緩沖模塊的通信

CPLD與SRAM組成的緩沖通信模塊,即如何乒乓讀寫SRAM機制。設定一個讀寫標志FLAG,當一塊SRAM寫滿一幀圖像時,FLAG會出現“1”到“0”或者“0”到“1”的跳變,同時切換數據流的流向,寫另一塊SRAM,同時切換輸出至后級DAC的數據流;如此循環,軟件流程圖如圖6所示。

圖6 緩沖模塊通信軟件流程圖

評論