DDS信號源的FPGA實現

通過分析,DDS可由下列兩次變換實現:

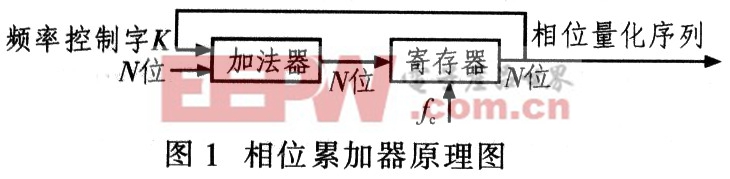

(1)變量K產生量化的相位序列 該過程一般由一個以上作時鐘的Ⅳ位相位累加器實現,如圖1所示。本文引用地址:http://www.104case.com/article/192016.htm

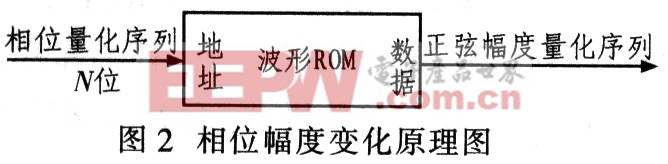

(2)離散量化相位序列產生正弦信號離散幅度序列 該過程是由式(8)的映射關系所構成的波形ROM尋址完成的,如圖2所示。把量化的數字波形經模數轉換,再通過低通濾波器LPF得到頻率為fc的余弦信號。變量K稱為相位增量(也叫頻率控制字)。當K=1時,DDS輸出最低頻率(即頻率分辨率)為fc/2N。因此,只要N足夠大,DDS可以得到很細的頻率間隔。要改變DDS的輸出頻率,只要改變頻率控制字K即可。DDS的最大輸出頻率由Nyquist采樣定理決定,即fc/2,也就是K的最大值為2N-1。

DDS可以很容易實現正弦信號和余弦信號正交兩路輸出,只需用相位累加器的輸出同時驅動固化有正弦信號波形的ROM和余弦信號波形的ROM,并各自經數模轉換器和低通濾波器輸出即可。

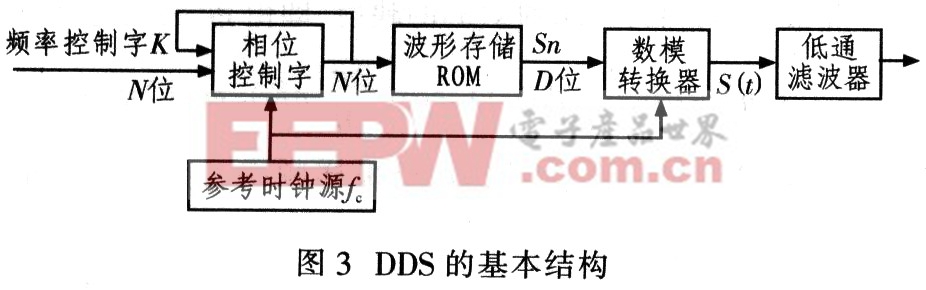

2.2 DDS的基本結構

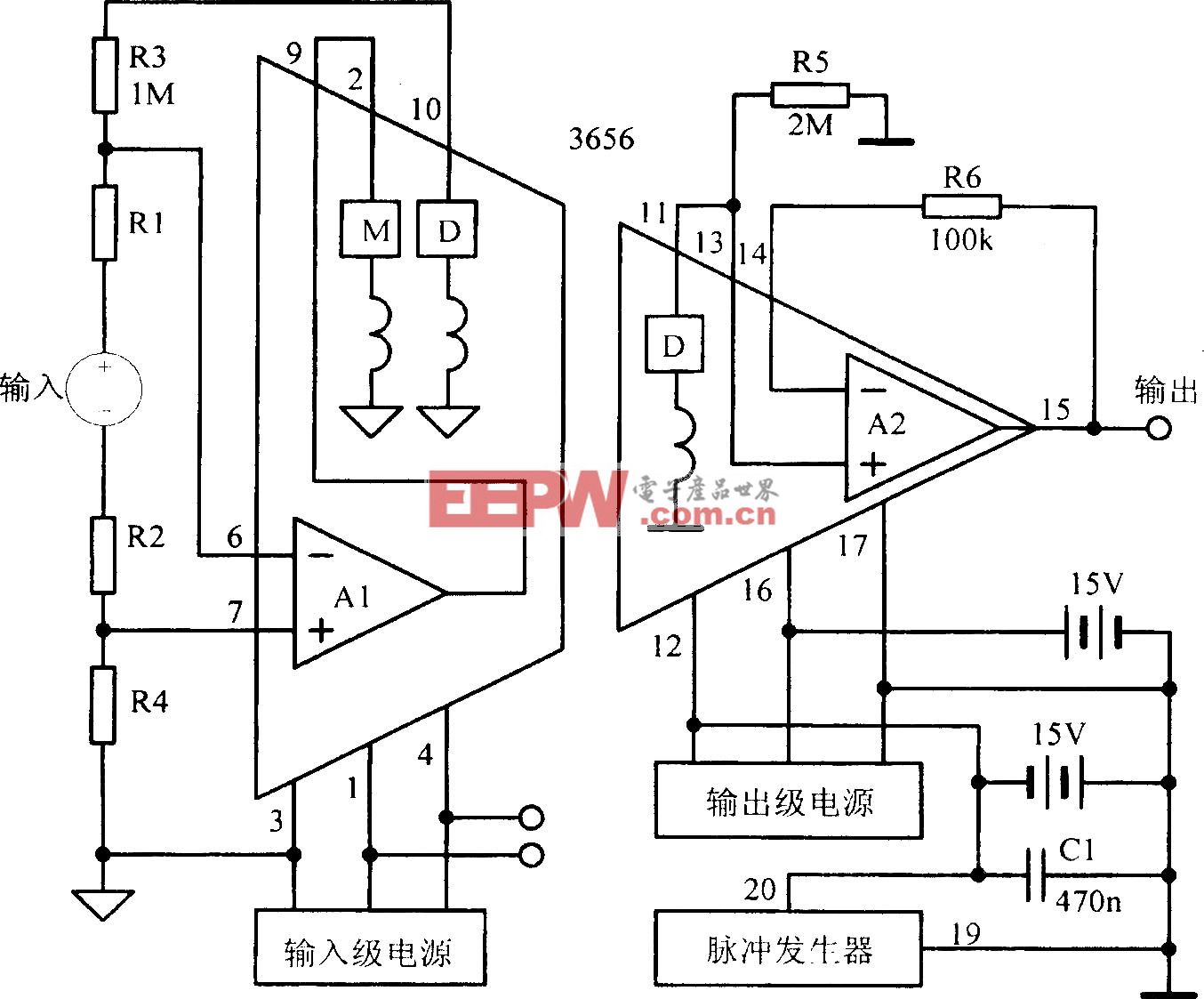

DDS包括數字和模擬兩部分,其主要由相位累加器、ROM波形查詢表、數模轉換器和低通濾波器LPF構成。DDS的基本結構如圖3所示,其中K為頻率控制字、f為時鐘頻率,N為相位累加器的字長,D為ROM數據位數及D/A轉換器的字長。相位累加器在時鐘fc/2的控制下以步長K為累加,輸出N位二進制碼作為波形ROM的地址.對波形ROM尋址,波形ROM輸出的幅值碼S(n)經數模轉換器轉換成模擬信號后再經LPF輸出。

3 應用設計

該系統設計是針對DDS的基本結構,以FPGA為核心,并與外圍電路而實現的。

3.1 相位累加器

相位累加器由8位加法器與8位寄存器級聯構成。累加器將加法器在上一個時鐘作用后所產生的相位數據反饋到加法器的輸入端;使加法器在下一個時鐘作用下繼續與頻率控制字(K)相加,實現相位累加,當相位累加器累加結果等于或大于256時,則產生一次溢出,返回到初始狀態,完成一個周期波形輸出。該相位累加器采用VHDL語言設計實現。

3.2 波形存儲器

以相位累加器輸出數據作為波形存儲器的取樣地址。進行波形的相位一幅碼轉換,即可在給定的時間上確定輸出的波形的抽樣幅碼。Ⅳ位的尋址RAM相當于把0°~360°的正弦信號離散成具有2個樣值的序列,若波形存儲器有D位數據位,則各樣值的幅碼以D位二進制數值保存在該模擬ROM(FlexlOKl0的RAM)中,按照不同地址輸出相應相位的正弦信號的幅碼數值。

DDS中的波形存儲器模塊用Ahera的F3exl OK系列中的RAM實現,選用Flexl0K10,Flexl0K10中共有3塊RAM,每塊大小為2 K位,可構成2 048x1,1 024×2,512x4,256x84種類型。該設計取N=8,D=8,波形數據運用高級語言C編制,相應數據保存于FPGA的RAM中。

3.3 D/A轉換電路的實現

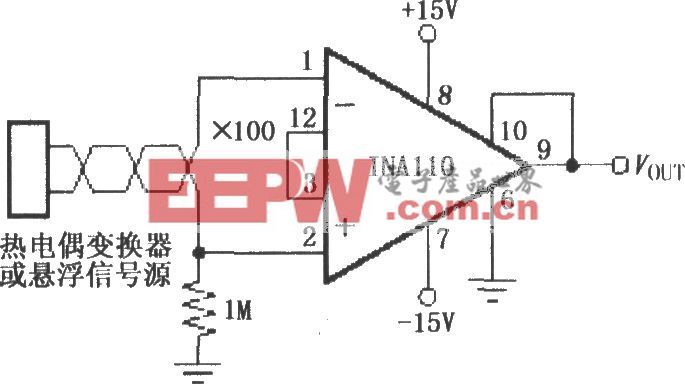

D/A轉換器的作用是把已合成的正弦波的數字量轉換成模擬量。正弦幅度量化序列經D/A轉換后變成包絡為正弦波的階梯波s(t)。

該單元選用數模轉換器DAC0832,使其工作于雙緩沖器方式,并強制片選信號(Cs)、寫信號1(R1)、寫信號2(R2)、數據傳送信號(XFER)為低電平,將F:PGA輸出的數據轉換成相應模擬量。

評論