改進型CIC抽取濾波器設計與FPGA實現

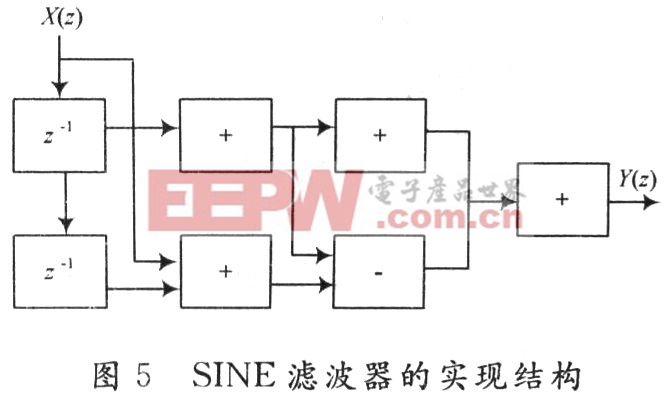

最后,非遞歸結構中每一級再采用多相技術進一步降低功耗。考慮到中間第二、三、四級階數比較高,因此將每級分解實現,相當于引進流水線技術,提高電路速率。第二級與第四級均為10階,分解為2個5階級聯的結構,第三級為14階,分解為5階、4階、5階。這樣除了SINE濾波器,整個改進型濾波器只有(1 +z-1)4與(1+z-1)5兩種結構。這種高度規則的結構使電路設計和版圖設計變得更加容易。SINE濾波器放在最后一級如圖5所示。

4 仿真結果

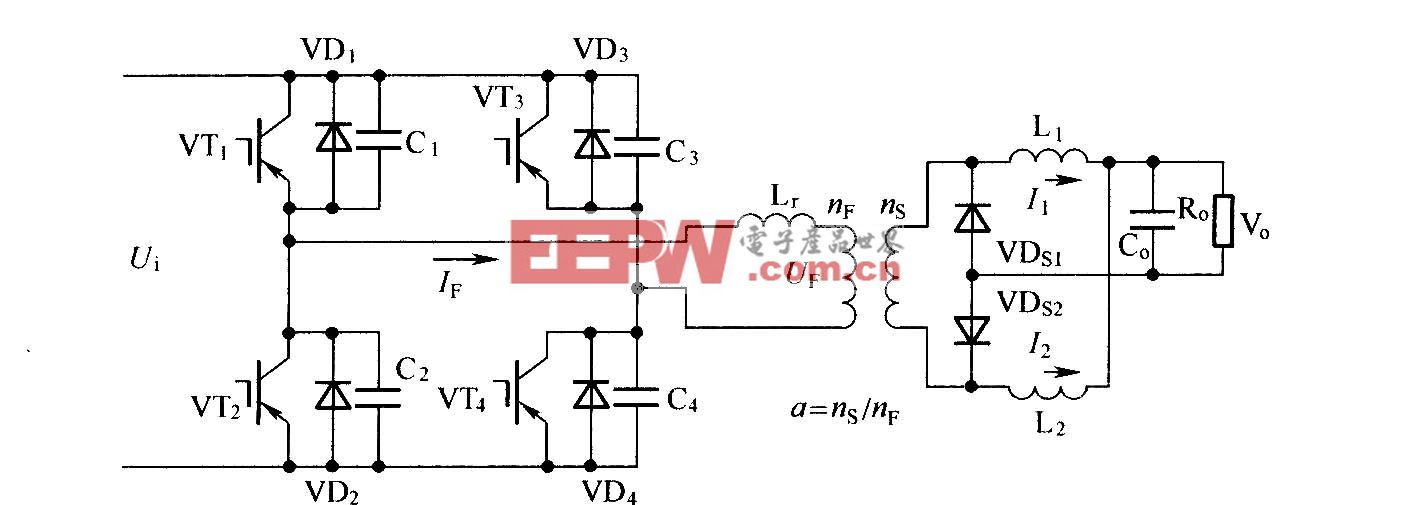

為了快速有效地驗證濾波器性能,使用Matlab的simulink工具搭建了三階sigma-delta調制器,輸入各種頻率的正弦波產生高速1,0信號,作為CIC濾波器的輸入。改進型CIC濾波器FPGA實現是采用Xilinx公司SPARTAN-3系列開發板,在ISE 6.3環境下進行的。為了進行比較,分別采用文獻[4]中給出的轉換抽取結構與圖4、圖5給出的改進結構實現。頂層結構與仿真結果如圖6所示(其中clk 為輸入時鐘;rst_n為復位信號,也可視為使能信號,低電平有效;data_in為1 b的輸人數據;data_out為47 b補碼輸出;data_en為輸出數據變化指示信號)。

根據FPGA綜合報告,采用文獻[4]中電路結構實現的改進型CIC,使用的邏輯資源為1 704.個,占器件總資源的88%,而采用圖4、圖5中的優化電路結構時,在濾波性能不變的前提下,使用的邏輯資源減少為1 261個,占器件總資源的65% ,說明對結構的改進與優化大大節省了硬件資源。

5 結 語

這里在文獻[4]的基礎上提出一種改進型的CIC濾波器,大大提高了其通帶特性,相較于傳統CIC濾波器,無論在阻帶還是通帶特性都有明顯改善,適合應用于高精度∑-△模數轉換器中。在FPGA實現的過程中,對文獻[4]中的結構進行優化,使部分電路工作在更低的頻率下,大大降低了功耗;采用非遞歸結構,結合傳輸函數自身的特性合并部分分式,降低了電路復雜性;在每級處理時僅采用加法器和延時單元,節省了硬件資源,提高了實用性。

評論