改進型CIC抽取濾波器設計與FPGA實現

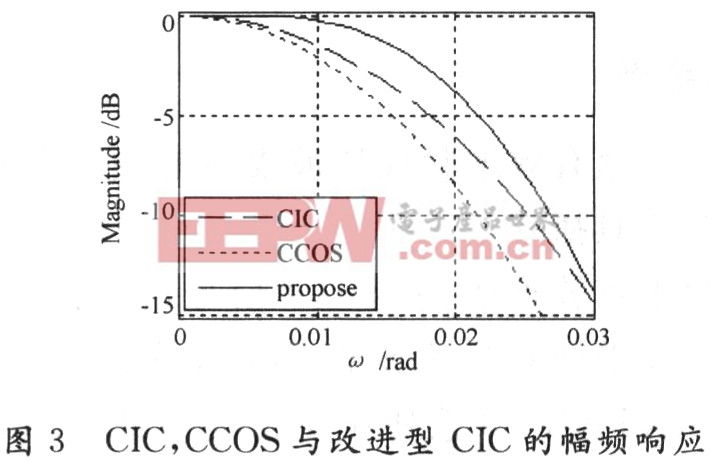

圖2(b)為M=32的四階CIC濾波器與新結構的濾波器(CCOS)幅頻響應對比。式(5)中取k1=4,k2=k3=2;n1=2,n2=n3=4。從圖2中可以看出CIC濾波器第一旁瓣相對于主瓣衰減為52.94 dB,而CCOS的旁瓣衰減則達到101.9 dB。如果達到相同的阻帶衰減,CIC至少高達8階,其實現電路將會非常龐大。本文引用地址:http://www.104case.com/article/192006.htm

圖2(c)對上述兩種濾波器主瓣曲線放大,從圖中明顯可以看出CCOS濾波器通帶特性比CIC變差。取濾波器的通帶截止頻率為fc=1/8M(Fs為歸一化值),CIC通帶衰減為O.129 3 dB;CCOS為0.286 7 dB。

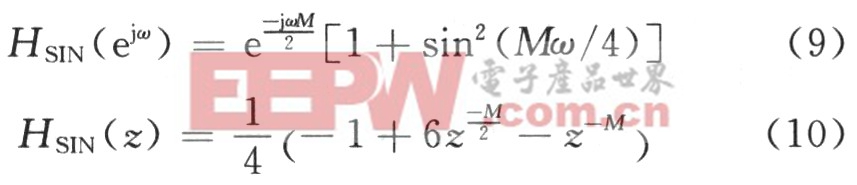

為了進一步提高CCOS的通帶特性,對文獻[4]提出的CCOS進行改進,在其后級聯一個SINE濾波器,其幅頻特性與傳輸函數如下:

式中:M必須為偶數,這樣才能避免分數延時。出于節省功耗的目的,取M為抽取值的2倍,這樣SINE濾波器即可在提取到抽取之后,將計算量降為原來的 1/M,該結構通過移位和加法即可實現,無需乘法器。圖3為改進型CIC(取M=64)與CCOS,CIC的幅頻特性曲線比較,可以看出改進的CIC濾波器的通帶特性得到明顯改善。由于補償濾波器的引入,阻帶衰減為100.3 dB,但通帶衰減僅為O.000 1 dB.

3 改進型CIC的FPGA實現

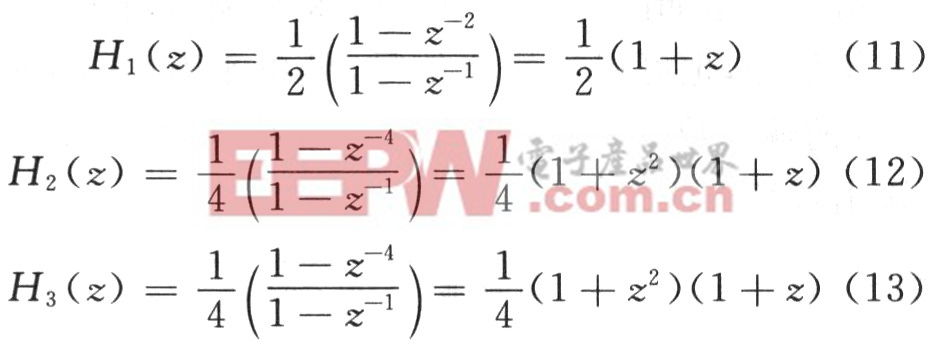

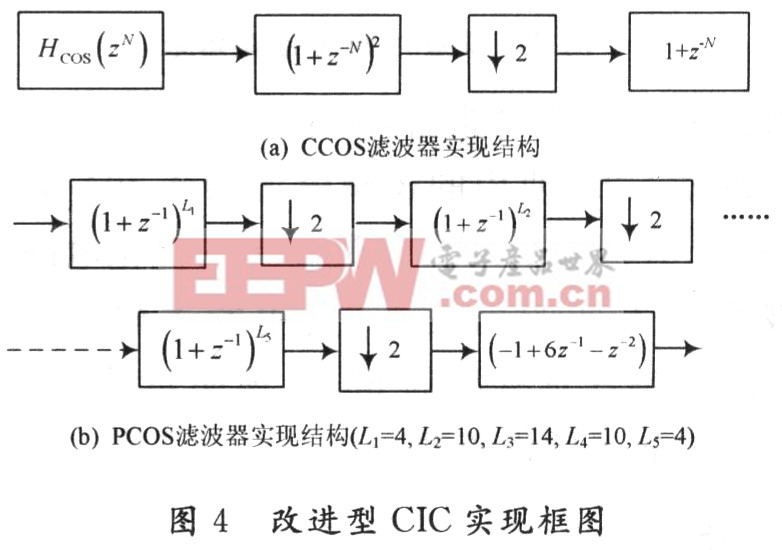

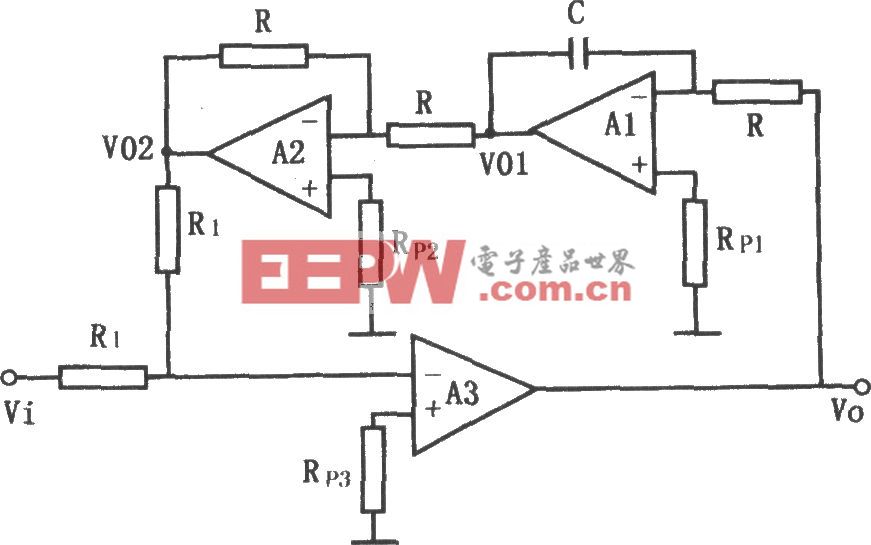

按照式(5)中CCOS各級聯部分的關系,文獻[4]中給出一種電路實現結構圖,通過抽取使部分電路工作在更低頻率。為了進一步提高濾波器設計的功耗使用效率,減小占用芯片的面積,對文獻[4]的結構進行再次改進和優化。通過改變算法運算的具體步驟,來減少運算的步數,從而提高濾波器的效率。

首先把遞歸結構實現的部分改為非遞歸算法結構,降低功耗;

其次把CCOS濾波器的部分電路再次抽取降頻,處理后每級表達式都可以與非遞歸算法結構的表達式合并,既可以使CCOS濾波器部分電路工作在低頻降低功耗又可以大大減少存儲單元數量。CCOS濾波器實現結構如圖4(a)所示,圖4(b)為對CCoS濾波器抽取改講后整體改進型濾波器的結構。

評論