有效防止FPGA設計被克隆的技術

DesignTag工作原理本文引用地址:http://www.104case.com/article/192003.htm

DesignTag是一個小型低成本IP內核,可以內置在FPGA中作為設計的一部分。它是一種帶唯一代碼(“簽名”)的數字內核,可以從外部識別,而無需讀取FPGA比特流或內部寄存器。

它的工作原理是以一種預先定義好的方式調制主器件的功耗。微小的熱脈沖能以很低的衰耗透過芯片封裝傳播。功率“浪涌”電平被選中以提供只有約0.1℃的封裝溫升。額外增加的典型功耗值是5mW,而中等規模的Spartan FPGA的正常功耗通常大于150mW,這意味著這個標記信號遠低于噪聲電平。

DesignTag默認情況下在工作15分鐘后關閉(用戶可修改這個時間),這樣做有兩個作用。首先,它消除了少量增加的功耗。其次,它使剽竊者的檢測更加困難。DesignTag也可以被FPGA中發生的內部事件觸發,這種事件可以是發送ID代碼或指示內部狀態,或是故障條件的一條指令。

DesignTag數據庫

所有DesignTag的代碼數據都保存在中央數據庫中。用戶可以選擇將他們的代碼“公開”或“隱蔽”。公開列表的優勢在于所有DesignTag閱讀軟件都可以檢測這些代碼,從而允許用戶、執行代理或合同廠商確認被測器件(DUT)的有效性。

相比之下,當用戶不希望任何第三方知道他們的產品是否被打上了標記時,隱蔽代碼是最好的選擇。在這種情況下,代碼由用戶分發到受信任方,只有安裝了這些代碼的閱讀軟件才能檢測出相應的標記。

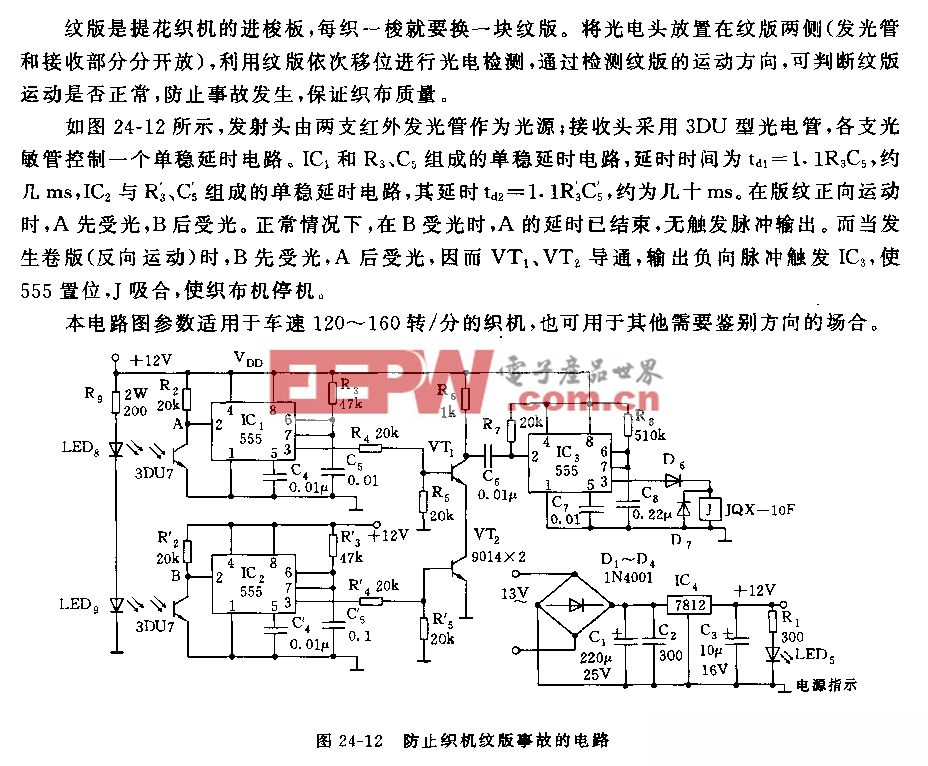

將DesignTag集成進FPGA

在FPGA中使用的這種IP內核被實例化為HDL代碼,形成一個用Verilog或VHDL編寫的“黑盒”。可供交付的內容包括,用于驅動熱量輸出的內置代碼以及電路要求的I/O引腳。全數字設計的尺寸很小,一般在賽靈思的Spartan 3 FPGA中只占用256個片(slice)。

基于安全性考慮,這種內核只提供加密過的EDIF網表。該IP采用了多種技術來阻止“反向工程”,并且能夠將自己隱蔽起來防止受到篡改或檢測。DesignTag內核很大程度上獨立于用戶設計,因此對設計流程的影響很小。

圖2:DesignTag提供了“偷竊證據”。

DesignTag采用2~250MHz范圍之內的一個輸入時鐘來驅動工作時序。這個時鐘應來源于系統內的任何有效時鐘,而不能是專門為標記IP內核產生的時鐘。最主要的原因是最低成本因素,它還能通過并入系統來迷惑檢測或中止標記功能的企圖。

DesignTag的控制輸入可以由嵌入式系統驅動,或在設計階段設置為默認值。例如,標記內核可以根據需要設置為連續發送;也可以在上電后的一段規定時間內發送,然后進入待機模式。還有另外一個選項,即發送序列可以在任何時間由一個觸發脈沖(Trigger)輸入端來啟動。

標記內核可以許可最多4個不同的內置代碼,這可以通過代碼選擇 (Code Select) 輸入端進行選擇。嵌入式系統可以對這個內核進行編程,讓它根據要求發送其中一個代碼來指示內部狀態條件。例如,指示內存發生溢出或檢測到軟故障條件,整個過程不會中斷系統功能。

篡改輸出(Tamper output)信號可以從DesignTag送入嵌入式系統,這有兩個好處。第一,它能用作削弱系統性能的去激活信號,并通過翻轉配置比特流中的隨機比特來迷惑取消標記功能的企圖。第二,如果攻擊者對比特流實施反向工程來重建設計,由于DesignTag塊看起來像是設計的有機組成部分,因而無法被識別。

評論