基于DSP+CPLD 可重構數控系統的設計與仿真

(2).四軸編碼器信號處理電路設計

四軸編碼器信號處理電路是對光電編碼器輸出的兩組相差90o 的方波信號的處理,從而獲得執行元件實際位置,其輸出是一路16 位的數字量,反饋給中央處理器,編碼器信號處理電路包括濾波,倍頻,計數幾個功能模塊,傳統的四軸編碼器信號處理電路采用分立元件來設計,它可靠性、抗干擾能力差,應用CPLD 設計了單片并行四軸編碼器信號處理電路。

它具有實時性好,硬件體積小,工作效率高,提高系統的集成度,相對于分立元件,單片并行四軸編碼信號處理電路集成在一個片子上,一方面單片芯片內的門電路、觸發器的參數特性是完全一致的,在相同轉速下脈沖信號的脈沖周期可以保持一致。另一方面,電路做在單個芯片內,抗干擾性能比分離器件構成的電路也有很大的提高,增強了系統的靈活性、通用性和可靠性。本文設計是一個四軸伺服系統,因此有八路四組方波信號,A 相B相相差90o,CLR,CLK,WE 分別為輸出清零,系統時鐘和輸出使能,SEL*是輸出選擇信號,選擇X,Y,Z,A中的一組信號處理的結果作為輸出信號,分時送到數據總線。

濾波模塊的設計

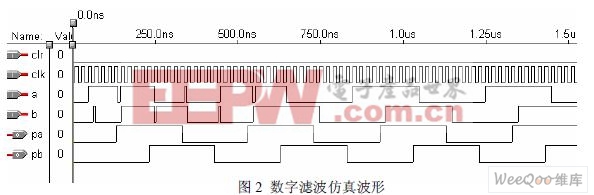

編碼盤理論上是穩定的方波信號,但在實際操作中,經常會存在脈動干擾,濾波模塊的功能是將這些脈動干擾濾掉,降低系統產生誤動作的可能性,提高系統的可靠性,下面的VHDL 程序通過對A,B 兩相方波信號同時延時四個CLK 脈沖,,脈沖寬度小于三個CLK脈沖周期的輸入信號被濾掉。仿真結果如圖:

倍頻計數模塊的設計

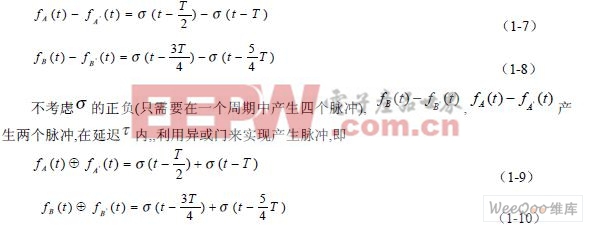

四倍頻電路的設計是為了增加計數脈沖在一個周期中的個數,來提高測量的分辨率,工程中常把光電編碼器輸出的兩路方波信號的上升沿和下降沿,來獲得四倍頻的脈沖信號,把光電編碼器的分辨率提高四倍,通過光電編碼器輸出兩路方波信號相差的正負來確定運動的方向,對光電編碼器輸出信號A、B;可以寫成:

如圖:

伺服電機相關文章:伺服電機工作原理

評論