FPGA多接口功能在航姿計算機中的應用

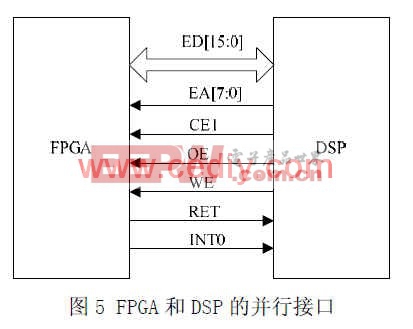

(4)與 DSP的并行接口。并行接口是最常用的一種通訊方式之一。FPGA和DSP之間的數據通訊通過 16位并行接口完成(原理圖如圖5)。首先,根據 DSP的時序,系統上電后需要對DSP進行不小于 200ms的復位。在系統正常工作時期,當 WE=0寫有效、CE1=0片選有效、 a21=1數據有效時,FPGA從總線上讀取 DSP的數據,當 OE=0讀有效, CE1=0片選有效, a21=1數據有效時,FPGA將數據放在總線上等待 DSP讀取。FPGA讀、寫數據都根據 DSP的 EA信號來標識所操作的數據地址。雖然系統中的數據量比較大,但是為了提高實時性和可靠性,在FPGA中沒有使用 FIFO或者 RAM來存儲數據,而只是用 FPGA中的變量來臨時存儲,本設計中也最終證明了該設計的可用性,這樣也讓 FPGA的硬件資源更合理利地得以使用。

本文引用地址:http://www.104case.com/article/191969.htm

本文引用地址:http://www.104case.com/article/191969.htm3整體時序的實現

本系統的實時性和復雜性對于正確實現總體時序和工作邏輯提出了比較大的挑戰。現從以下幾個方面說明本設計的實現方法:

1 高速實時性。總體的并行設計,各個通訊模塊幾乎完全獨立地工作,互不占用資源,從而使得高效性和實時性的要求得到了極大地滿足。

2 總體時序有序。該航姿計算機的整體時序和整體邏輯都是讓 FPGA中的頂層實體來控制實現的。系統大致時序和邏輯如下:上電后,FPGA控制系統完成各部件的上電自檢后,各接口開始并行工作,按照自己的工作時序接收、發送數據。其中,IMU數據大約每 10ms發送一次,FPGA每次接收完 IMU數據后,與 DSP通過并行接口進行一次通訊。FPGA將最新的傳感器測量值發送給DSP,而 DSP將最新的航姿信息回傳給 FPGA,最終FPGA通過 ARINC429接口傳給外部。這樣的設計保證了系統時序穩定、邏輯可靠。

3 數據準確性。數據的準確也要求考慮到具體硬件上的問題。由于 FPGA中的邏輯門是有時間延遲的,在這樣實時的系統中就必須嚴格考慮門電路的延時,否則,很容易出現如下類似的一些問題,例如,把剛接收到一組測量數據賦給變量是需要幾納秒到十幾納秒的時間來穩定的,如果此時正好遇上操作改變量的時鐘觸發,偶爾就會引起野值數據,這些不確定的野值隨時可能造成整個航姿結算的錯誤,因此需要根據具體時序修改,以保證杜絕這類問題。

該系統的 FPGA設計已經經過模擬數據仿真試驗、跑車試驗得以驗證,在數據準確性、實時性方面都得到了較好的滿足。

評論