基于FPGA的AES算法芯片設(shè)計(jì)實(shí)現(xiàn)

其中Round1-Round3、FinalRound是由組合邏輯完成的操作,都能夠在一個(gè)時(shí)鐘周期內(nèi)執(zhí)行完成。這種風(fēng)格的代碼在生成流水線電路時(shí),還需要控制指令的配合。

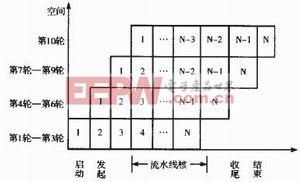

圖3是拆分輪運(yùn)算的流水線時(shí)空?qǐng)D。圖中數(shù)字表示數(shù)據(jù)分組的序號(hào),整個(gè)流水線操作由啟動(dòng)、發(fā)起、流水線核、收尾和結(jié)束5部分組成,當(dāng)進(jìn)入流水線核時(shí)的效率是最高的。

圖3 拆分輪運(yùn)算的流水線時(shí)空?qǐng)D

用加速比(Speedup)可以衡量采用流水結(jié)構(gòu)之后加密過程相對(duì)于非流水結(jié)構(gòu)速度的提高。計(jì)算流水線加速比的基本公式為![]() 。

。

設(shè)加密N個(gè)分組,10輪運(yùn)算每輪的運(yùn)算時(shí)間為!,則

![]()

當(dāng)N的取值無限增大時(shí),這個(gè)比值將接近于3.33…。因而使用流水結(jié)構(gòu)數(shù)據(jù)處理速度比非流水結(jié)構(gòu)提高到3倍多。

仿真實(shí)驗(yàn)和結(jié)果

圖4為加密過程時(shí)序。針對(duì)128bit明文分組和128bit初始密鑰的AES算法,在QuartusII軟件下,采用中間相遇的設(shè)計(jì)方法將頂層模塊化圖形設(shè)計(jì)與底層VHDL語言描述相結(jié)合實(shí)現(xiàn)。實(shí)驗(yàn)時(shí)選用APEX20KE系列的EP20K1500EFC33-3為目標(biāo)芯片進(jìn)行仿真和功能驗(yàn)證。密鑰裝載完畢之后每加密輸出一個(gè)分組需3個(gè)時(shí)鐘周期,吞吐率為689.500Mbits/s。使用了3056個(gè)LUTs,81626個(gè)Memorybits,可以滿足SDH標(biāo)準(zhǔn)速率STM-4規(guī)定的622.080Mbits/s的要求。

|

圖4 加密過程時(shí)序

結(jié)合FPGA的結(jié)構(gòu)特點(diǎn),本設(shè)計(jì)實(shí)現(xiàn)的IP核具有如下特點(diǎn):接口設(shè)計(jì)靈活,外部接口的設(shè)計(jì)和定義可以根據(jù)不同加密芯片的接口設(shè)計(jì)要求現(xiàn)場改動(dòng)。資源占用小,脫密電路采用與加密電路部分復(fù)用的結(jié)構(gòu)實(shí)現(xiàn),從而節(jié)省了資源。設(shè)計(jì)支持重用,在算法實(shí)現(xiàn)頂層設(shè)計(jì)時(shí)采用了模塊化設(shè)計(jì)方法,結(jié)構(gòu)清晰,可以根據(jù)不同的功能需求進(jìn)行改動(dòng),利于設(shè)計(jì)重用

評(píng)論