用FPGA技術實現模擬雷達信號

前言

本文引用地址:http://www.104case.com/article/191955.htmFPGA(現場可編程門陣列)是由掩膜可編程門陣列和PLD(可編程邏輯器件)演變而來的,并將二者的特性結合在一起,使FPGA既有掩膜可編程門陣列的高邏輯密度和通用性,又有PLD的可編程特性。FPAG技術的發展使得單個芯片上集成的邏輯門數越來越多,能實現的功能越來越復雜。它以編程方便、集成度高、速度快等特點受到電子設計人員的青睞。人們可以通過硬件編程的方法設計和開發ASIC(專用集成電路)芯片,極大地提高芯片的研制效率、降低開發費用。

通過應用FPGA技術,較好地為“某型雷達告警設備”的配套檢測儀器實現了模擬雷達信號發生器ASIC芯片的設計,該芯片能夠提供“某型雷達告警設備”測試過程中所需的多種典型的重頻脈沖及制導信號等,其中包括SA-6重頻信號、SA-2重頻脈沖及制導信號、SA-3重頻脈沖及制導信號、雷達脈沖視頻等。所設計的ASIC芯片的性能較為理想。

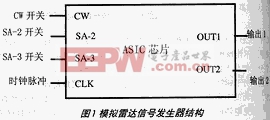

模擬雷達信號發生器的結構如圖1所示。可以看到,模擬雷達信號發生器由連續波雷達模擬信號CW開關、制導信號SA-2開關、制導信號SA-3開關、時鐘脈沖產生器、輸出1、輸出2和產生模擬雷達信號的控制芯片組成。上述開關都是高電平有效,開關的消抖動電路放在控制芯片部分考慮。時鐘脈沖產生器由外部的晶體振蕩器產生一個頻率穩定的1MHz時鐘脈沖,用來滿足信號脈沖寬度的要求。“CW開關”有效時,“輸出2”輸出連續波雷達達模擬信號;“SA-2開關” 有效時,“輸出2”輸出SA-2的重頻脈沖,“頻脈沖,“輸出1”輸出SA-2的指令信號組;“SA-3開關”有效時,“輸出2”輸出SA-3的重頻脈沖,“輸出1”輸出SA-3的指令信號。

ASIC芯片的設計

1芯片主要性能指標

(1)產生連續波雷達模擬信號:重頻3012Hz,脈寬1μs±0.1μs;

(2)產生制導信號SA-2重頻脈沖:重頻2463Hz,脈寬0.5μs±0.1μs;SA-2指令信號組:重頻2463Hz,每秒132個單指令,44個指令組,指令脈寬1μs±0.1μs;

(3)產生制導信號SA-3重頻脈沖:重頻3497Hz,脈寬0.5μs±0.1μs;SA-3指令信號同SA-3重頻脈沖等。

評論