SAW傳感器后端信號處理電路的設計

在設計中,通過兩位量程選擇開關的控制,對時鐘信號進行分頻,可以得到1 s,100 ms,10 ms和1 ms四個不同的閘門開通時間。同時,計數(shù)部分采用六位十進制計數(shù),于是可以得到0.1~100 MHz四個頻率檢測量程。

2.3 仿真及其測試

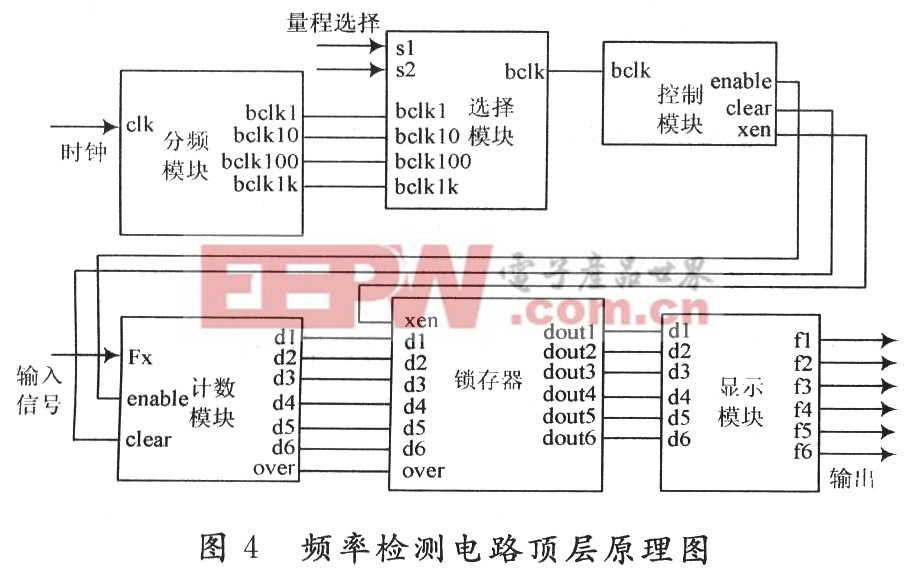

利用VHDL語言對電路的各個子模塊編寫相應的代碼,并用EDA軟件QuartusⅡ對源程序進行了編譯、優(yōu)化、邏輯綜合,自動地將VHDL語言轉換成門級電路,進而完成了對電路的分析、驗證、自動布局布線、時序仿真、管腳鎖定等各種工作。最終所設計的頂層電路如圖4所示。該電路結構中,clk為系統(tǒng)的時鐘信號;Fx為輸入的檢測信號;s1,s2為整個電路的量程選擇控制輸入端。通過s1, s2可以控制頻率檢測電路檢測范圍。

最后,采用了Altera DE2開發(fā)板,將設計的電路下載到硬件電路中,從而完成了對整個頻率檢測電路的設計工作,并利用函數(shù)發(fā)生器對電路進行了驗證。在2 MHz左右的測試結果如表1所示。

3 結 語

本文設計了一種SAW傳感器中的信號處理電路,對該電路中的頻率檢測部分,利用了FPGA技術,使頻率檢測的范圍和精度滿足了傳感器的要求。通過對所設計電路的計算機仿真和實驗,驗證了設計的信號處理電路的可行性。

評論