基于FPGA的正交數字混頻器中數控振蕩器的設計與實

z表示第次旋轉時與目標角度之差,n次旋轉后,式經次迭代可以得到以下結果z輸入,通過、兩式的迭代運算,迭代結果輸出的n和n就是所需要的三角函數值。

FPGA實現

1是數控振蕩器的頂層電路結構。可以看到,頻率控制字寄存器將接收到的的頻率控制字送入相位累加器,相位累加器對系統時鐘進行計數,每到達輸入頻率控制字的值即對相位進行累加,隨后將累加值送入相位相加器,與相位控制字寄存器接收到的初始相位相加,得到當前的相位值。其中,相位累加器是決定性能的一個關鍵模塊,可以利用器件的進位鏈實現快速、高效的電路結構。然而由于進位鏈必須位于臨近的邏輯陣列塊和邏輯單元內,所以長的進位鏈會減少其它邏輯使用的布線資源;同時,過長的進位鏈也會制約整個系統速度的提高。因此,設計中采用進位鏈和流水線技術相結合的辦法。采用以上做法實現的相位累加器既能保證具有較高的資源利用率又能大幅提高系統的性能和速度。

/余弦相位序列,將此序列送入基于算法的波形發生器,最終獲得兩路正交的正余弦輸出序列。

CORDIC運算迭代單元,然后在系統時鐘的驅動下,將本級的輸出作為本級的輸入,通過同一級迭代完成運算。這種方法雖然很直觀但是為了將計算結果提供給下一級運算,會占用大量的寄存器資源,帶來許多額外的資源消耗。而且其最大的缺點是運算速度較慢需要個時鐘周期才能輸出一個數據,不利于數據的高速實時處理。

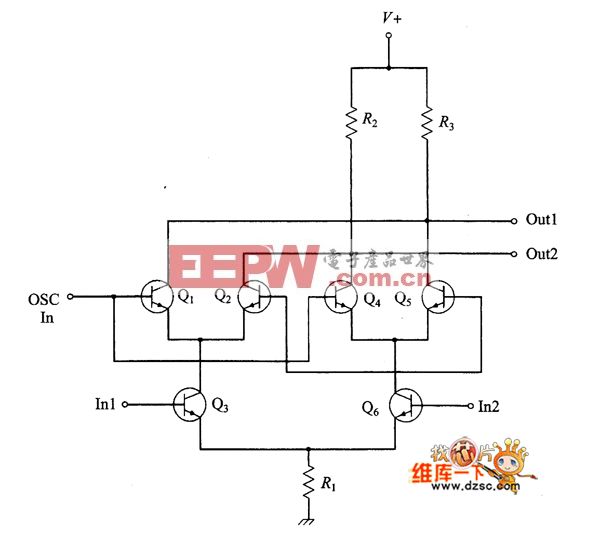

2所示的由級運算單元組成的流水線結構,正常工作時只需一個時鐘周期就能輸出一個數據,為數據實現高速實時處理提供了保障。每一級實現的功能是根據式進行一次迭代,移位的位數等于當前的迭代級數,加減法選擇由該級中的最高位符號位決定,得到下一級的、和的值。經過級流水線運算后,的值變為,和的值則為初始值0的余弦和正弦值。每一級電路結構主要包括兩個移位器和三個加減法器,arctan(2),可將該小數轉換為二進制數后,保存于存儲單元中,為每一級流水線提供查找表。

n級迭代序列:,則迭代所能覆蓋的角度范圍僅有的迭代,將迭代序列擴展從而使角度覆蓋范圍也擴大。

Altera公司的軟件,采用對上述數控振蕩器結構進行描述,在上通過功能仿真,結果正確后綜合出電路網表,最后將程序下載至器件780C6中實現。

Stratix器件,該器件的位加減器工作頻率可以達到以上,從而為產生高速的正交信號提供高速可靠的工作時鐘。考慮到的工作時鐘瓶頸是在相位累加器,因此可以根據具體需要縮減相位累加器的位數來提高的工作時鐘頻率。本文設計的工作時鐘為,相位累加器的位數為位,輸入的頻率控制字為,根據公式: ,,其中為輸入的頻率控制字,clk為工作時鐘,為相位累加器位數,可算出輸出的正余弦信號的頻率out=30MHz,頻率分辨率。頻率分辨率說明:通過輸入頻率控制字來改變輸出正余弦信號的頻率時,可以達到的最小步進。另外,也可以根據實際需要的頻率改變輸入頻率控制字值。當然,輸出頻率的上限要受到定律的限制,即out的最大值為clk/2,實際設計一般不大于clk。

3為數控振蕩器的部分仿真時序圖。

FPGA器件中利用迭代算法產生正余弦信號。可以看到,該數控振蕩器不但省去了傳統龐大的存儲器資源,僅用移位寄存器和加法器就可產生正余弦信號,結構簡單,非常適用于在正交數字混頻器中進行高速高精度的數字調制解調。

評論