基于FPGA的PLL頻率合成器設計

3.3 檢測較高頻的整數/半整數分頻

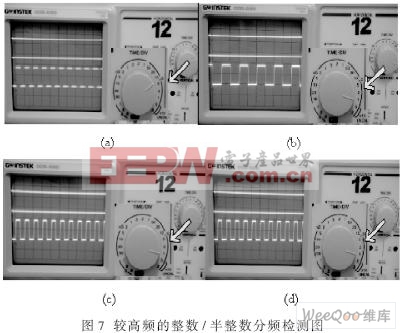

當N為更高的數值時,通過比較CD4046的輸入輸出波形,很難直接看出來。這時輸入仍采用1kHz的頻率值,這時直接看輸出的頻率值。N=100、500、999、999.5時的波形分別如圖7(a)、(b)、(c)、(d)所示。

由圖7(a)得:所測頻率為1/(10×10-6)Hz=100 kHz

由圖7(b)得:所測頻率為2/(10×10-6)Hz=500 kHz

由圖7(c)得:所測頻率約為1/(10×10-6)Hz=1 MHz

由圖7(d)得:所測頻率約為1/(10×10-6)Hz=1 MHz

可見,這時實測值與理論上預見的結果也是一致的。

3.4 誤差分析

較低頻時的波形之所以占空比不是標準的50%,是由于CD4046輸出頻率經過FPGA分頻模塊之后產生的反饋信號只是一個脈沖信號,這個脈沖信號要與出入CD4046的1kHz的標準信號進行相位比較,而標準信號的占空比是50%,這就造成了相位比較之后產生的信號波形占空比不是50%,而本系統測試時所采用的是模擬示波器,對較低頻占空比非50%的顯示不是很好,這很有可能是由于波形不是非常標準的主要原因。

在測試完成之后,又用數字示波器來專門檢測CD4046的輸出頻率,結果與理論計算幾乎吻合。

本系統結合FPGA技術、鎖相環技術、頻率合成技術,設計出了一個整數/半整數頻率合成器,輸出范圍為1 kHz~999.5 kHz,步進頻率可達到0.5 kHz;與以前的實驗裝置相比,系統在性能指標、直觀性等方面都有所提高,它不僅可以用于教學實驗,還可以用作頻率源、頻率計。

評論