基于FPGA的PLL頻率合成器設計

工作過程中,FPGA控制可預置的N/N+0.5的變化,當N/N+0.5變化時,輸出信號頻率響應跟著輸入信號變化。同時FPGA也實現了鍵盤掃描與液晶顯示的功能。

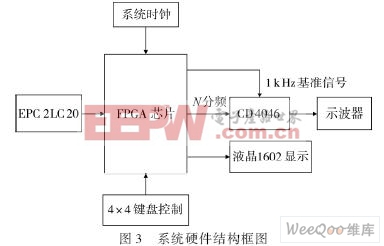

2.1 系統(tǒng)硬件設計

硬件上,如圖3所示。該系統(tǒng)部分主要由7大部分組成:外部系統(tǒng)時鐘、4×4鍵盤控制電路、FPGA處理芯片、EPC2LC20型EPROM芯片、PLL芯片CD4046及其外圍電路、液晶1602顯示模塊、示波器。本設計使用FPGA專用配置芯片EPC2,通過下載電纜ByteBlaster MV,把程序多次下載到FPGA芯片中。系統(tǒng)使用FPGA芯片作為控制中心,按鍵掃描輸入控制信息,液晶屏進行顯示,能夠方便直觀地演示PLL芯片CD4046在頻率合成技術中的應用,且達到了預期的指標要求。本設計中的主要硬件的具體型號是:液晶TC1602A-01T,FPGA芯片EPF10K10LC84-4,40.000 MHz有源晶振HO-12B。

2.2 系統(tǒng)軟件設計

通過編寫VHDL程序實現整數/半整數分頻,并應用Quartus II和ModelSim,筆者完成了VHDL程序的設計及仿真。

系統(tǒng)軟件功能框圖如圖4所示。

系統(tǒng)的具體工作過程如下:

鍵盤掃描模塊負責掃描按鍵,輸出鍵值,鍵值輸入到1602液晶模塊中進行顯示。同時,通過功能鍵模塊去控制鍵值輸入到FPGA中的分頻模塊中,功能模塊為“確定”時,鍵值輸入到FPGA分頻模塊中,分頻系數N就等于輸入的鍵值。功能模塊為“清除”時,FPGA分頻模塊中,分頻系數N就會被清零。

3 系統(tǒng)測試及結果

測試儀器:INSTEK GOS-620(20 MHz模擬示波器)

測試溫度:室溫

3.1 檢測系統(tǒng)是否入鎖

鍵盤輸入從1~999.5時,所測CD4046的1號管腳波形如圖5所示,指示PLL處于入鎖狀態(tài)。

3.2 檢測較低頻的整數/半整數分頻

當N=3、9、13、1.5、5.5、9.5,輸入為1 kHz的頻率時,CD4046的輸出波形分別如圖6(a)、(b)、(c)、(e)、(f)、(g)所示。從圖中可以很明顯地讀到,輸出分別為3 kHz、9 kHz、13 kHz、1.5 kHz、5.5 kHz和9.5 kHz。這與理論上預見的結果是一致的。

評論