基于FPGA的高速SDRAM控制器的視頻應用

當要求寫SDRAM時,控制狀態機的狀態由c_tRCD2跳變到c_WR狀態,發出寫命令。SDRAM控制器會在發寫命令的同時將本次突發數據的第一個數據送到總線上,接著是三個周期的狀態:c_tDAL1、c_DAL2、c_tDAL3,之后回到c_idle狀態。這樣完成了寫數據的一次循環,剛好需要 8個周期。在回到c_idle狀態后即可啟動下一次寫數據傳輸,這時狀態機跳到c_ACT狀態,發出激活另一個bank的某一行的命令,然后經過兩個周期后,此時上一次寫操作的數據突發長度剛好結束。下一個周期狀態變成c_WR,發下一次的寫命令,同時將這一次突發長度的第一個數據放到SDRAM數據總線上……如此循環,可以完成長度是1280的連續數據的寫入。這個循環如何結束呢?當發了最后一個突發寫命令后,狀態機回到c_idle時,即可停止循環,不再進入激活狀態。總之通過控制這個狀態機可以完成長度是8的倍數的連續數據讀寫。控制狀態機還有實現刷新操作的功能,當要求對SDRAM進行刷新操作時,控制狀態機的狀態會跳變到c_AR,SDRAM控制器會依此發出刷新命令。然后狀態機跳變到c_tRFC狀態等待刷新操作的結束。當刷新操作結束后,狀態機將恢復到c_idle。這樣就完成了一次刷新操作。如果需要多次刷新,就可以連續進行多次這樣的循環。

2.3 SDRAM控制器的綜合

本設計使用的SDRAM芯片是MT48LC2M3282,FPGA芯片是cyclone的EP1C6Q240C6。綜合工具是QuartusII 6.0。綜合的結果是邏輯單元使用了170個,占總資源的3%;工作頻率最高可以達到240.10 MHz,滿足項目要求。本文引用地址:http://www.104case.com/article/191928.htm

3 代碼的仿真測試

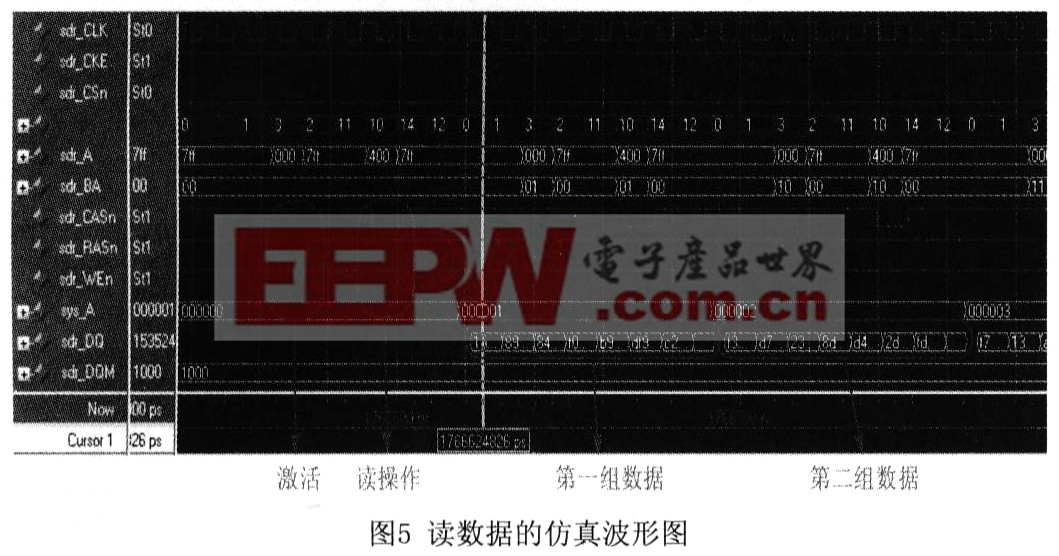

本設計的仿真工具是Modelsim6.1f,部分仿真測試波形見圖5。圖中描述了讀一行數據的時序圖,在開始突發寫數據后,SDRAM的數據總線sdr_DQ上的數據沒有被中斷。這個表示整個設計達到了能夠支持超長數據突發讀寫功能,能滿足設計要求。

4 結束語

本文介紹了一種實現超長數據突發讀寫的設計。此設計采用切換Bank操作節約了激活命令所花費的時間;采用自動預沖命令節約了預沖命令所花費的時間;采用集中刷新完成了足夠的刷新操作。通過對上面操作的組合設計,能夠很好地完成超長數據的突發讀寫。在設計中,成功地實現了突發長度是1280的數據讀寫,滿足了項目需求。

評論