基于FPGA的高速SDRAM控制器的視頻應用

刷新命令是對SDRAM內的數據完成再生的操作,因為SDRAM采用電容存儲數據,而電容存在漏電的現象,因此需要隔一段時間對電容作一次刷新(即重新充電),一般來說要求64ms內將SDRAM的所有行都刷一遍。SDRAM有兩種刷新命令:自動刷新和自刷新。自刷新是在芯片處于低功耗狀態下時才使用的方式,芯片內部自動完成刷新操作。自動刷新是控制器發起的刷新操作,它必須在SDRAM沒有激活行時才能進行刷新操作,而且需要占用一定的時間(大約 60~70ns)。控制器可以根據需要選擇在何時刷新,即定時刷新,或集中刷新。定時刷新是隔一段時間就刷新一次;集中刷新是在某一段空閑時間內連續刷新若干次。這個只要保證在64 ms內將所有的行都刷一遍即可,具體的刷新方式可以根據自己的應用需要來設計。本文引用地址:http://www.104case.com/article/191928.htm

2 SDRAM控制器的設計

2.1 SDRAM控制器的設計思路

SDRAM芯片完成一次讀寫操作由三個命令組成:激活、讀/寫、預沖。讀寫數據的突發長度往往是有限制的,在SDRAM芯片本身提供的突發長度最大只能達到一行的容量(256,即全頁突發模式)。這樣當一次讀寫突發長度結束后,如果需要發起下一次讀寫,就需要發預沖命令結束這一行,然后發激活命令開啟下一行。這樣才能開始寫下一次數據。因此,如果想要連續的數據讀寫,就必須想辦法節省激活和預沖命令。

激活命令通過切換Bank操作來完成。SDRAM有4個獨立的bank,每一個bank可以同時允許有一行激活,彼此并不會相互干擾。這樣的話,在同一時刻最多可以有4個行處于激活狀態。這就為節約激活時間提供了解決方案:在突發讀寫一個bank下的某一行時,可以在突發長度結束之前提前激活另一個 bank下的某一行。這樣當這個突發長度結束時就可以直接讀寫另一bank中被激活的行。預沖可以采用自動預沖方式來完成,不需要額外的預沖命令。

通過上述兩種操作方式可以完全實現超長突發長度的數據讀寫,本設計將SDRAM設置成突發長度為8,突發長度結束后采用自動預沖方式完成此行的預沖操作,具體設想如下:

在寫SDRAM時,先激活Bank0的第一行;發出帶自動預沖模式的寫操作;數據開始寫入這一行內;一段時間后(在突發長度結束之前)將Bank1的第一行激活;在Bank0的寫突發長度結束的同時,發出寫Bank1的命令,這樣接下來的數據就寫入Bank1的第一行中;而由于在寫SDRAM的Bank0 時設置成自動預沖模式,所以SDRAM會在Bank0的寫操作結束后自動預沖,經過tRP(預沖時間)后,這一Bank自動回到idle狀態。同樣 Bank1處于寫突發長度時將Bank2的第一行激活,在Bank1的寫突發長度結束的同時發出寫Bank2的命令……如此四個bank輪流工作,將數據均勻地分配到4個bank中。

對于這種超長的數據突發讀寫,完成一次讀寫操作所花費的時間比較多,例如讀寫時鐘是108MHz時,一次突發長度是1280的寫操作所花費的時間是11. 6 μs,即在這段時間內SDRAM的數據總線是不能被中斷的。因此采用集中刷新是最好的解決辦法。在突發讀寫結束后,會有一段比較長的空閑期(具體時間長度根據視頻數據的視頻中行消隱數據個數和讀寫時鐘決定),在這段時問內可以集中連續發出多個刷新命令,只需要保證在64ms內總的刷新次數達到了要求即可。

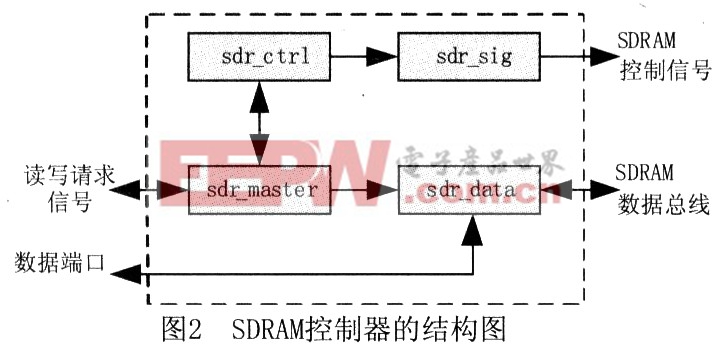

2.2 SDRAM控制器的實現

本設計中將SDRAM控制器分成4個子模塊:sdr_master主控模塊、sdr_ctrl命令模塊、sdr_sig譯碼模塊、sdr_data數據通路模塊,見圖2。sdr_master主控模塊根據外部的讀寫請求向sdr_ctrl命令模塊提供各種讀寫控制信號;sdr_ctrl命令模塊內部的控制狀態機會依此發出各種SDRAM讀寫控制命令;sdr_sig譯碼模塊會把sdr_ctrl輸出的控制命令譯碼成符合SDRAM接口的信號。此SDRAM 控制器的設計,最復雜的部分在于如何設計SDRAM的工作時序,即SDRAM何時激活,何時讀/寫,何時預沖,何時刷新。這些控制除了滿足SDRAM的工作特性外,還要滿足設計要求。因此,鑒于SDRAM控制的復雜性,一般都采用狀態機來控制。本設計中sdr_ctrl命令模塊包括兩個狀態機:初始化狀態機完成SDRAM的初始化;控制狀態機完成SDRAM的正常工作控制。下面分別詳述這兩個狀態機的設計。

初始化狀態機的結構見圖3。系統在上電(復位)后,處于i NOP狀態;當等待了100 μs后,狀態跳轉到i PRE,發出預沖命令;接著跳轉到i tRP等待;經過tRP時間后,狀態跳轉到i_AR1,發第一次刷新命令,然后在i_tRFC1等待tRFC時間后發第二次刷新命令,再等待tRFC;接下來轉到狀態i MRS,發裝載模式字命令,然后等待tMRD時間后初始化完成,進入i_ready狀態。至此初始化完成,SDRAM芯片就可以正常工作了。

控制狀態機的狀態跳變見圖4。此狀態機是為了滿足超長數據的連讀或連寫而特殊設計的。上電后處于c_idle狀態,當初始化完成后,控制狀態機才能開始正常工作。當外部要求進行讀寫操作時,會正式地啟動狀態機。此時狀態機跳變到c_ACT狀態,使SDRAM控制器發出激活命令;接下來兩個狀態 c_tRCD1、c_tRCD2是激活等待時間tRCD;然后狀態機根據外部是讀請求還是寫請求,來決定下一個狀態是發讀命令還是寫命令。下面以寫數據為例進行說明,讀數據的工作過程是一樣的。

評論