安全芯片中密碼算法的多IP核集成方法

⑥執行指令

MOV INSTRUCT,#00H

關閉SHA1協處理器,完成SHA1調用。

對TDES及RSA的功能調用類似于SHA1,僅在指令配置時稍有不同。TDES增加了密鑰生成過程的指令配置與完成信號判斷,RSA增加了對模長與模冪的參數配置。由上可知,與方法二相比較,IP橋接技術在調用實現IP核功能時,需要增加的僅為一條IP選擇參數配置指令。 本文引用地址:http://www.104case.com/article/191926.htm

3 測試與仿真

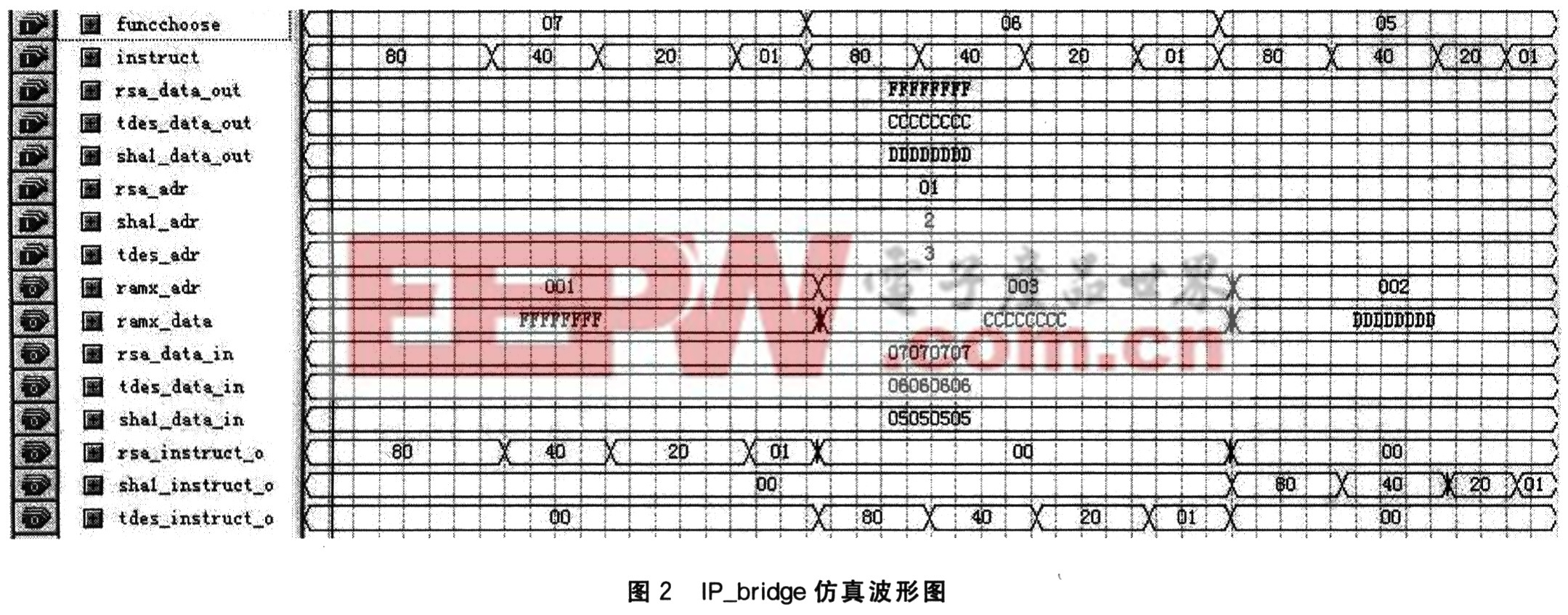

本文采用軟件仿真與FPGA下載測試兩種手段,對2.2中的設計進行了功能正確性驗證。圖2給出了該設計中IP_bridge在quartus II 5.0下的仿真波形圖。

在圖2中,FUNCCHOOSE為系統功能區的IP選擇參數輸入,INSTRUCT為IP控制指令。當IP選擇參數值為07H、06H、05H時,對應的選定IP為RSA、TDES、SHA1。以選定SHA1為例,當IP選擇參數為05H時,IP_bridge模塊重構asis_ramx為SHA1專用數據處理區,且此時SHA1控制指令shal_instruct_o被配置為當前IN-STRUCT值,完成對SHA1的接口配置;當IP選擇參數為 06H、07H時,IP_bridge置SHA1控制指令shal_in-struct_o為00H,使SHA1協處理器處于休眠狀態。對 IP_bridge仿真波形圖的分析表明,其邏輯功能正確。由于在初次FPGA下載測試時發現,允許IP_bridge對IP核進行時鐘配置會導致協處理器功能不穩定,因而取消了IP_bridge的IP核時鐘配置功能。除此以外,其余部分均滿足本文2.1中的功能要求。

為進一步驗證設計的正確性,本文選用Altera公司Cyclone II系列EP2C35F672C6器件,對其進行了FPGA下載測試。在初次測試時發現,各IP核雖然可以完成功能調用,但執行結果不穩定,測試結果的最后5~10字節與標準測試對的結果不符。經分析發現,導致IP核功能錯誤的原因為IP_bridge在對時鐘進行配置時,會產生時鐘延遲。因此,取消了 IP_bridge的時鐘配置功能,在Qu-artus II 5.0下進行編譯仿真與綜合下載,再次進行FPGA下載測試。測試結果顯示,各IP核功能均正確無誤。采用選定器件,IP_bridge邏輯資源消耗為 200 LE,最大路徑延遲為16.838 ns。

結 語

本文在總結多IP核集成設計方法的基礎上,提出了一種IP橋接技術,用于實現多IP核集成;并以其為指導,基于一個8位SoC系統,具體實現了三個IP核集成。功能仿真與FPGA測試表明該技術具備實際可行性,且相比較于現有多IP核集成方法,IP橋接技術具備可有效提高片內資源利用率,降低系統功耗與開發成本等優勢;其缺點在于,當不同IP核的數據接口不一致時,IP_bridge的邏輯設計會比較復雜,且不能實現對IP核的變頻時鐘配置。初步分析表明,通過修改IP核的雙端口存儲區數據寫入環節,延長數據寫入完成至done信號有效這一時間段,可解決這一問題。方法的有效性檢測與具體實現,是筆者下一步工作的重點研究內容。

評論