FPGA異步FIFO設計中的問題與解決辦法

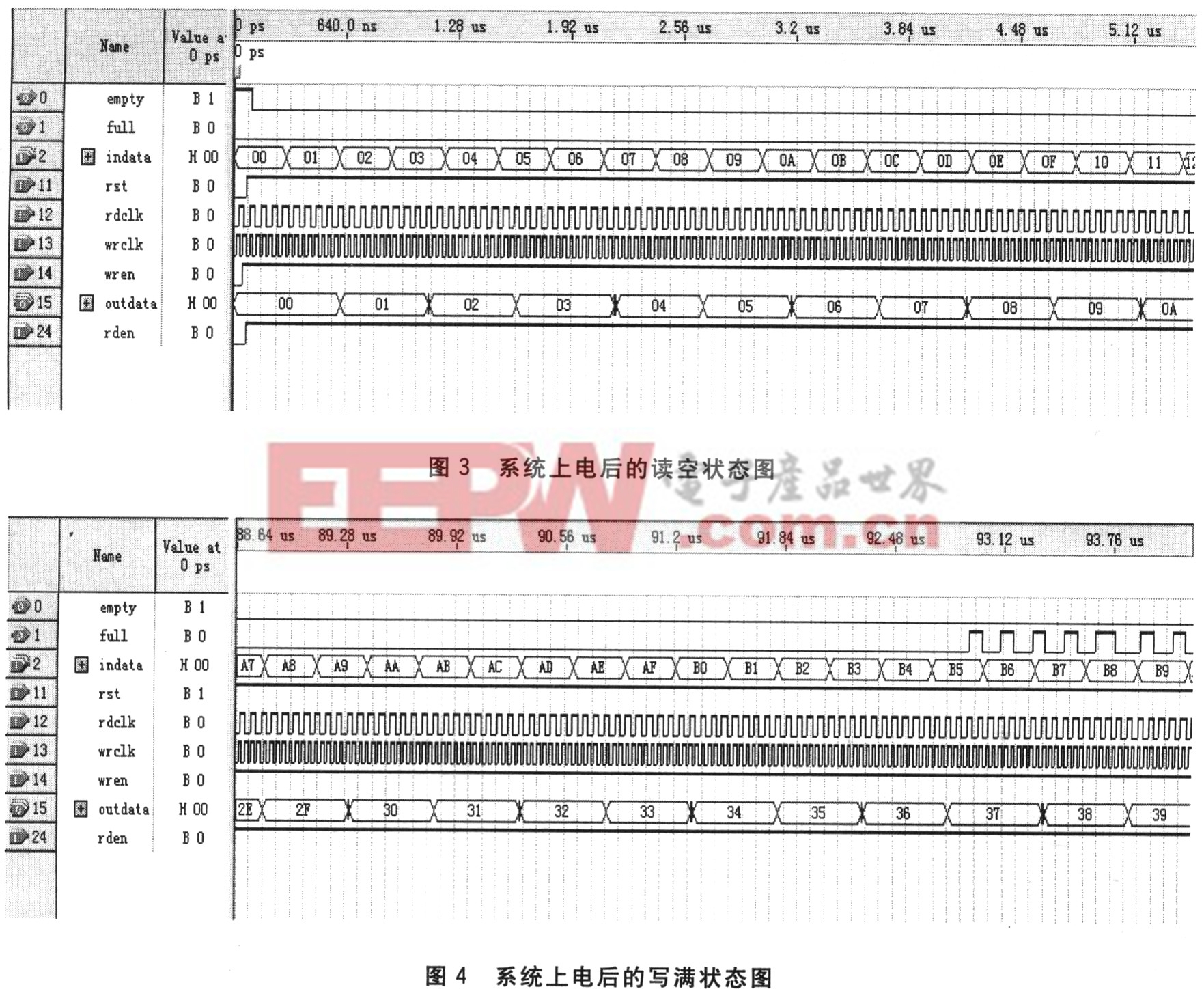

本系統采用QuartusIl8.1對系統進行仿真,由于系統深度較大,所以設定仿真時間為100 μs。系統剛上電時,雙端口RAM中暫時沒有數據,此時系統處于讀空狀態,empty變為高電平,full保持低電平,如圖3所示。隨著RAM中數據的不斷寫入,系統進入寫滿狀態,此時full變為高電平,而empty變為低電平,如圖4所示。本文引用地址:http://www.104case.com/article/191924.htm

結 語

本文根據異步FIFO設計的難點和要點,提出了具體的解決方案。在空/滿標志位產生條件的判斷上提出了“檢測+計數器”的新思路,使系統設計方便實用,并采用格雷碼方式降低了亞穩態出現的概率。通過驗證,這種方法在有效判斷空/滿標志位方面有很大的優勢。

評論