FPGA異步FIFO設計中的問題與解決辦法

2.2 空/滿標志位的判斷

為保證數據的正確寫入和讀出,不發生寫滿和讀空操作,怎樣判斷空/滿標志位的產生就成為異步FIFO設計的核心問題。異步FIFO是環形存儲的,當讀寫地址指針相等時,意味著空標志位或者滿標志位的產生。但是卻不能確定是寫滿還是讀空狀態。為解決這一問題,本文將轉換為格雷碼后的讀寫地址指針分別經過檢測和計數器。每當讀寫指針遍歷一圈(當讀寫地址指針指向雙端口RAM的最后一個地址)時,寫計數i加1,讀計數j加1。這樣寫滿狀態和讀空狀態的判斷就需要同時滿足兩個條件。下面分別給出寫滿和讀空狀態的判斷。

①寫滿狀態的判別:當讀地址指針等于寫地址指針,并且i>j時,產生滿標志。

②讀空狀態的判別:當寫地址指針等于讀地址指針,并且i=j時,產生空標志。

由于空/滿標志位產生的結構圖對稱,故本文只給出滿標志位產生的結構圖,如圖2所示。其中,主數i為寫地址指針遍歷的圈數,計數j為讀地址指針遍歷的圈數。本文引用地址:http://www.104case.com/article/191924.htm

從圖2中可看出,地址指針轉換為格雷碼后,經過檢測和計數環節,將讀寫地址和讀寫指針遍歷的圈數分別送入比較器進行比較,從而準確地產生滿標志位。

3 FPGA內部軟異步FIFO設計

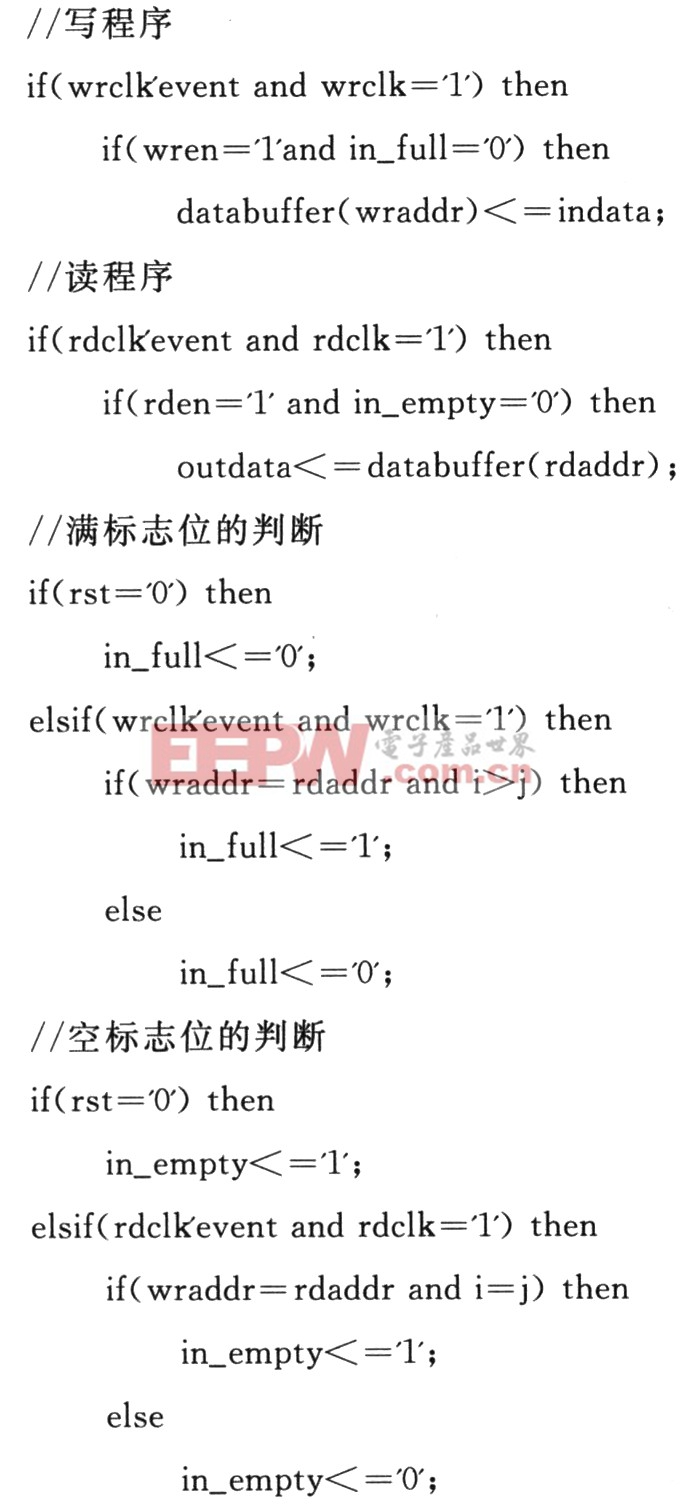

本設計中FPGA采用的是Xilinx Spartan3系列中的XC3S400PQ208。內部有56 Kb的分布式RAM和288 Kb的RAM,以及4個DCM(數字時鐘管理器)單元,為系統提供獨立的讀寫時鐘頻率。可以利用這些資源在FPGA內部實現異步FIFO模塊。本文采用 VHDL語言對雙端口RAM的讀寫操作進行編程,實現FPGA內部軟FIFO的設計。部分讀寫雙端口RAM和空/滿標志位的判斷源程序如下:

4 系統仿真

如果系統的讀時鐘頻率大于寫時鐘頻率,就有可能出現讀空的情況;如果系統的寫時鐘頻率大于讀時鐘頻率,就可能出現寫滿的情況。在實際系統中,一般都設置寫時鐘頻率大于讀時鐘頻率,故本文只考慮后一種情況。

評論