幀同步系統(tǒng)的FPGA設(shè)計(jì)與實(shí)現(xiàn)

1 引言

數(shù)字通信時(shí),一般以一定數(shù)目的碼元組成一個(gè)個(gè)“字”或“句”,即組成一個(gè)個(gè)“幀”進(jìn)行傳輸,因此幀同步信號(hào)的頻率很容易由位同步信號(hào)經(jīng)分頻得出,但每個(gè)幀的開頭和末尾時(shí)刻卻無法由分頻器的輸出決定。為此,幀同步的任務(wù)就是要給出這個(gè)“開頭”和“末尾”的時(shí)刻。通常提取幀同步信號(hào)有兩種方法:一類是在信息流中插入一些特殊的碼組作為每幀的頭尾標(biāo)記。另一類則不需要加入碼組,而是利用數(shù)據(jù)碼組本身之間彼此不同的特性實(shí)現(xiàn)同步。這里采取第一種方法――連貫式插人法實(shí)現(xiàn)幀同步。所謂連貫式插入法就是在每幀開頭插入幀同步碼。所用的幀同步碼為巴克碼,巴克碼是一種具有特殊規(guī)律的非周期序列,其局部自相關(guān)函數(shù)具有尖銳的單峰特性,這些特性正是連貫式插入幀同步碼組的主要要求之一。因此,這里提出幀同步系統(tǒng)的FPGA 設(shè)計(jì)與實(shí)現(xiàn)。

2 幀同步系統(tǒng)的工作原理

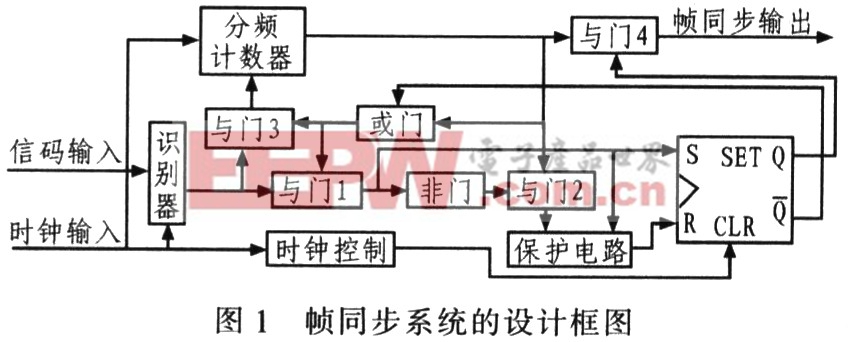

實(shí)現(xiàn)幀同步的關(guān)鍵是把同步碼從一幀幀數(shù)據(jù)流中提取出來。本設(shè)計(jì)的一幀信碼由39位碼元組成。其中的巴克碼為1110010七位碼,數(shù)據(jù)碼由32位碼元組成。只有當(dāng)接收端收到一幀信號(hào)時(shí),才會(huì)輸出同步信號(hào)。幀同步系統(tǒng)的設(shè)計(jì)框圖如圖1所示。

幀同步系統(tǒng)工作狀態(tài)分捕捉態(tài)和維持態(tài)。同步未建立時(shí)系統(tǒng)處于捕捉狀態(tài),狀態(tài)觸發(fā)器Q端為低電平,一旦識(shí)別器輸出脈沖,由于Q端為高電平,經(jīng)或門使與門1輸出”1”,同時(shí)經(jīng)或門使與門3輸出也為”1”,對(duì)分頻計(jì)數(shù)器模塊清零。與門1一路輸出至觸發(fā)器的S端,Q端變?yōu)楦唠娖剑c門4打開,幀同步輸出脈沖。系統(tǒng)由捕捉態(tài)轉(zhuǎn)為維持態(tài),幀同步建立。

當(dāng)幀同步建立后,系統(tǒng)處于維持態(tài)。假如此時(shí)分頻器輸出幀同步脈沖,而識(shí)別器卻沒有輸出,這可能是系統(tǒng)真的失去同步,也可能是偶然干擾引起的,因此在電路中加入一個(gè)保護(hù)電路。該保護(hù)電路也是一個(gè)分頻計(jì)數(shù)器,只有在連續(xù)若干次接收不到幀同步信號(hào)時(shí),系統(tǒng)才會(huì)認(rèn)為同步狀態(tài)丟失,由于丟失同步的概率很小,因此這里系統(tǒng)設(shè)置分頻計(jì)數(shù)器值為5,也就是說連續(xù)5幀接收不到幀同步信號(hào),系統(tǒng)才認(rèn)為丟失同步狀態(tài)。當(dāng)然分頻值可設(shè)置其他值,但該值越大,同步維持態(tài)下漏識(shí)別概率也越大。與門1的一路輸出置5分頻器的使能端,使之開始計(jì)數(shù),當(dāng)計(jì)數(shù)滿時(shí)會(huì)輸出一個(gè)脈沖使?fàn)顟B(tài)觸發(fā)器置零,從而無幀同步信號(hào)輸出,同步電路又進(jìn)入捕捉態(tài)。

評(píng)論