基于FPGA的PC/104-CAN通訊板設計

1.2 FPGA設計

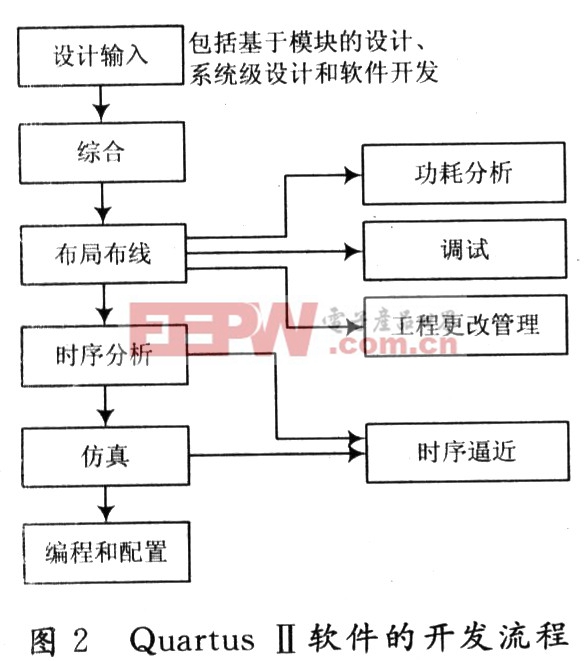

QuartusⅡ是Altera公司在21世紀初推出的FP-GA/CPLD開發環境,是Altera前一代FPGA/CPLD集成開發環境MAx+PlusⅡ的更新換代產品,其功能強大,界面友好,使用便捷。QuartusⅡ軟件集成了Al-tera的FPGA/CPLD開發流程中所涉及的所有工具和第三方軟件接口。QuartusⅡ軟件的開發流程如圖2所示。本文引用地址:http://www.104case.com/article/191897.htm

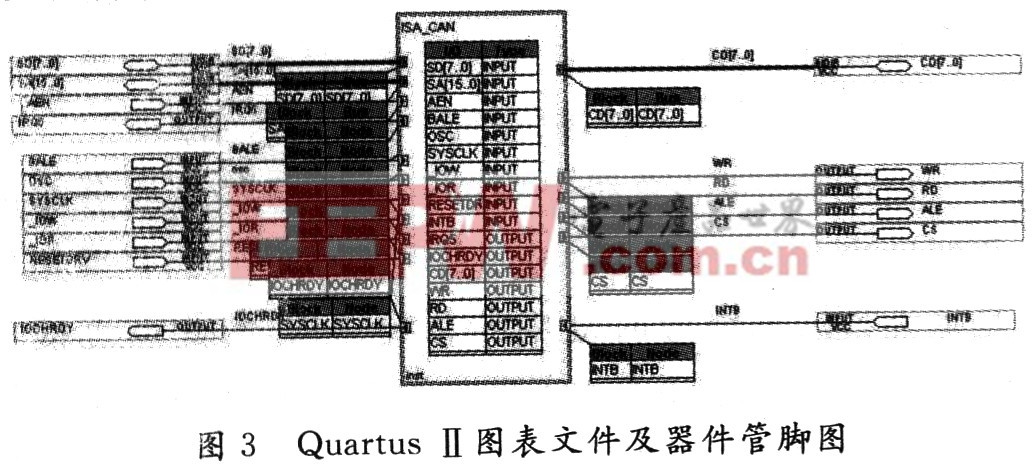

采用原理圖輸入和硬件描述語言相結合的方式,進行編譯后寫人器件中;同時可在線更改寫入內容,修改和調試簡單易行。FPGA的設計主要由兩部分組成:第一部分實現時序邏輯控制信號的轉換,第二部分實現地址譯碼和地址數據線的復用。QuartusⅡ圖表文件及器件管腳如圖3所示。

由于PC/104的地址總線和數據總線是各自獨立的,SJA1000T的地址總線和數據總線是分時復用的,所以它們之間不能直接相連,必須通過時序邏輯控制,再配合軟件來實現讀/寫操作。對SJA1000T的操作方法是:首先,對地址為CAN首地址+0(A2A1A0=000)的端口進行寫操作(WR為低,有效),CANALE為高,有效,此時復用的地址、數據總線上的數據被視為地址信號,進入SJA1000T內部鎖存器;然后,對地址為cAN首地址+1(A2A1A0=001)的端口進行讀或寫操作(RD/WR為低,有效),CANALE為低,上述中的地址信號已被鎖存,此時復用的地址、數據總線上的數據被視為數據信號,這樣即可完成對SJA1000T的各個寄存器和緩沖區的讀或寫操作。

1.3 硬件電路測試

主要檢測硬件結構及電路板設計是否正確。建立一個簡單的通訊連接,將兩個通訊板連接進行測試,用通訊板A作為輸出,通訊板B作為輸入。編程通過通訊板A發送數據,內容為8個隨機數,檢測通訊板B接收數據,如果不同則作加1計數。反之將通訊板B作為輸出,通訊板A作為輸入,進行相同測試。測試200萬次循環未見異常。

2 軟件設計

2.1 軟件流程圖

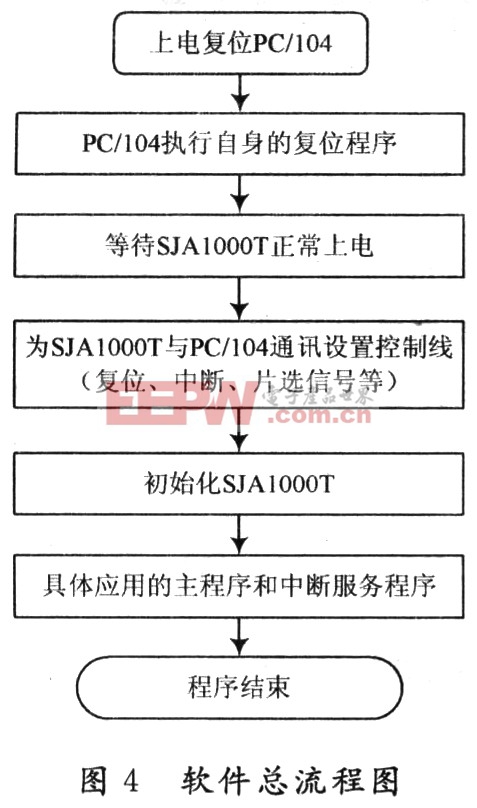

在該通訊板的設計中,控制部分的核心采用了PC/104嵌入式計算機系統。由于PC/104嵌入式計算機系統幾乎具有和一般的PC機一樣的強大功能,所以該通訊板的開發是在和系統模塊棧接在一起后,直接在嵌入式計算機上進行的。這些工作都是采用C語言進行編程設計的。采用C語言的優點在于其快速性、高效性。在利用嵌入式計算機強大資源的條件下,C語言能滿足模塊的實時性要求。在系統軟件的設計中,采用了結構化、模塊化的設計方法,滿足了儀器功能的要求。本接口系統的軟件任務基本為在CAN協議芯片SJA1000T有中斷發生時,根據SJA1000T的中斷寄存器的內容完成相應的操作(如發送、接收數據幀等)。其流程圖如圖4所示。

系統設計中要進行接口驅動程序的設計,為保證操作系統的穩定和安全,驅動程序必須按一定的規范來編寫。本系統的驅動程序主要考慮以下內容:設置端口和中斷號,設置通訊板通訊默認參數,通訊板內存分配,映射I/O地址,創建通訊板事件和數據接收事件,初始化中斷等。

SJA1000T初始化只有在復位模式下才能進行,初始化主要包括:工作方式的設置、接收濾波方式的設置、接收屏蔽寄存器和接收代碼寄存器的設置、波特率設置和中斷允許寄存器的設置等。SJA1000T在完成初始化后就可以回到工作狀態進行正常的通訊任務了。

評論