BP神經網絡圖像壓縮算法乘累加單元的FPGA設計

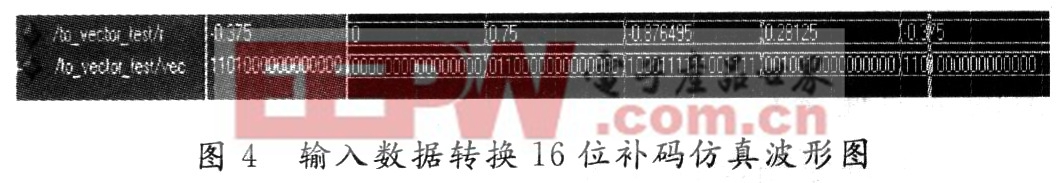

在本設計方案中,測試仿真平臺選用的FPGA芯片為ALTERA公司CycloneⅡ系列的EP2C8芯片,它采用90 nm的制造工藝,擁有8 256個邏輯單元,36個M4K隨機只讀存儲器,2個數字鎖相環,以及18個硬乘法器等豐富資源。仿真工具使用業界流行的MentorGraphics公司的仿真軟件Modelsim 6.1f。對設計進行驗證時,常見的方法是在模擬時施加輸入激勵信號,然后“讀”該設計的輸出信號,它的主要缺點是隨著模擬器的不同而不同。為了克服此缺點,采用的測試方法是用VHDL編寫一個測試模型發生器,稱為Testbench,它的優點是通用性好,靈活性強,可以隨時更改輸入激勵,已得到不同的仿真結果。在對該MAC模塊進行測試的過程中,涉及輸入數據的轉化問題,如前所述,在本神經網絡中,輸入數據歸一化后,集中在-1~+1之間,所以處理時必須進行轉化,最后采用16位補碼形式的定點二進制表示法,由于在求和中可能會產生溢出,還必須包含一個溢l出狀態信號。輸入數據轉換16位補碼的仿真波形如圖4所示。本文引用地址:http://www.104case.com/article/191891.htm

16位補碼轉換原輸入實數的仿真波形如圖5所示。

在完成了對輸入、輸出數據的轉換之后,編寫Testbench(測試臺)程序,對基于流水線設計的四輸入MAC進行行為級仿真,仿真波形如圖6所示。

綜上所述,在基于流水線的乘法設計中,雖然每一步操作后都加入了寄存器,消耗了更多的資源,但卻可以將系統延時降低到最慢步驟所需要的時間,極大地提高了同步電路的運算速度。

3 結 語

介紹了基于三層前饋BP神經網絡的圖像壓縮算法,提出了基于FPGA的實現驗證方案,詳細討論了實現該壓縮網絡組成的重要模塊MAC電路的流水線設計。在對BP神經網絡的電路設計中,對傳輸函數及其導函數的線性逼近也是近來研究的熱點之一,本文使用的壓縮查找表雖然能夠滿足設計要求,但仍然消耗了大量資源。該研究結果對整個壓縮解壓縮算法的實現以及多層神經網絡的相關研究工作提供了參考。

評論