模塊化FPGA設計在某雷達接收機中的應用

0 引言

目前基于FPGA和DSP結構的軟件無線電技術被廣泛應用在數字接收機設計中,雷達接收機領域的數字化技術也在日趨發展,如何借助數字化的軟硬件優勢設計出易實現、靈活,并滿足不同性能指標和目的的數字接收機成為工程設計的焦點。本文結合某連續波測速雷達數字接收機的設計實現,給出了一種基于模塊化的FPGA設計方案,并在此基礎上重點討論了信號處理模塊的設計。

1 雷達接收機概述

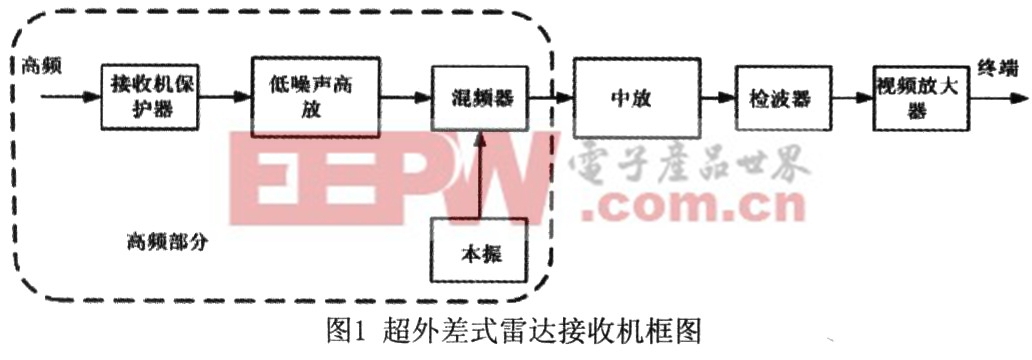

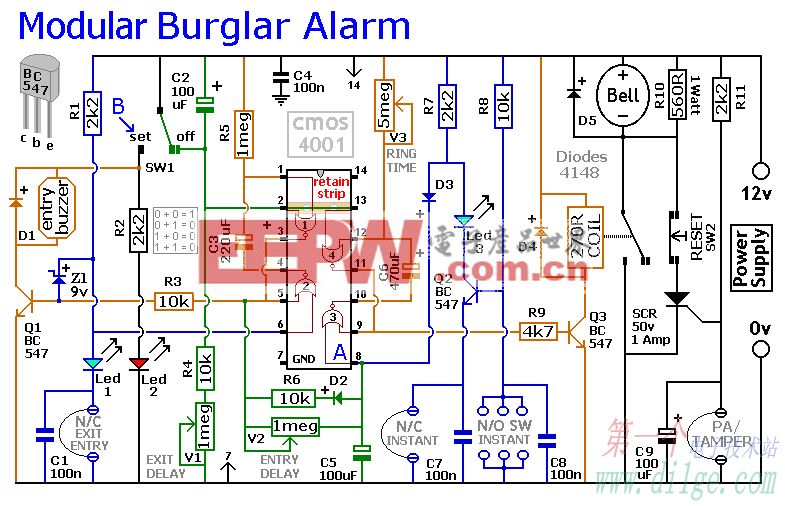

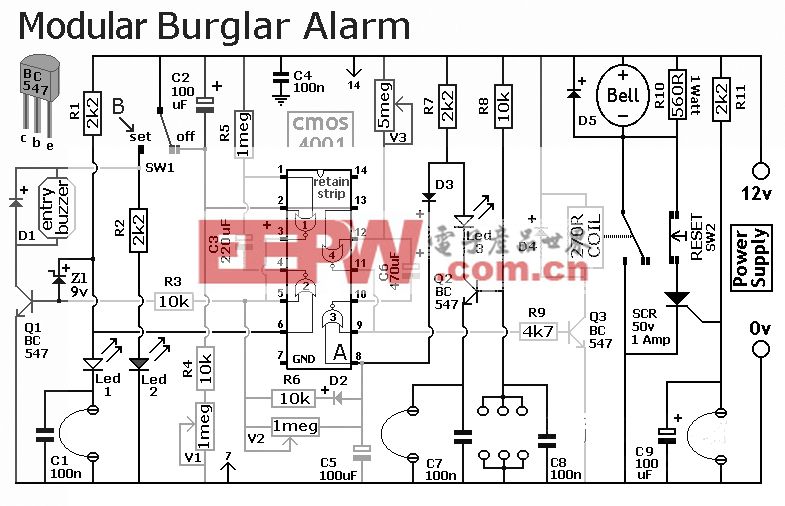

雷達接收機的任務是通過適當的濾波將天線上接收到的微弱高頻信號從伴隨的噪聲和干擾中選擇出來,并經過放大和檢波后,送至顯示器、信號處理器或由計算機控制的雷達終端設備。雷達接收機可以按應用、設計、功能和結構等多種方式來分類。但是,一般來說可以將雷達接收機分為超外差式、超再生式、晶體視放式和調諧高頻式等4種類型,其中超外差式雷達接收機具有靈敏度高、增益高、選擇性好和適用性廣等優點,實際中在很多的雷達系統中都獲得應用。超外差式雷達接收機的簡化方框圖如圖1所示。

2 數字中頻接收機原理

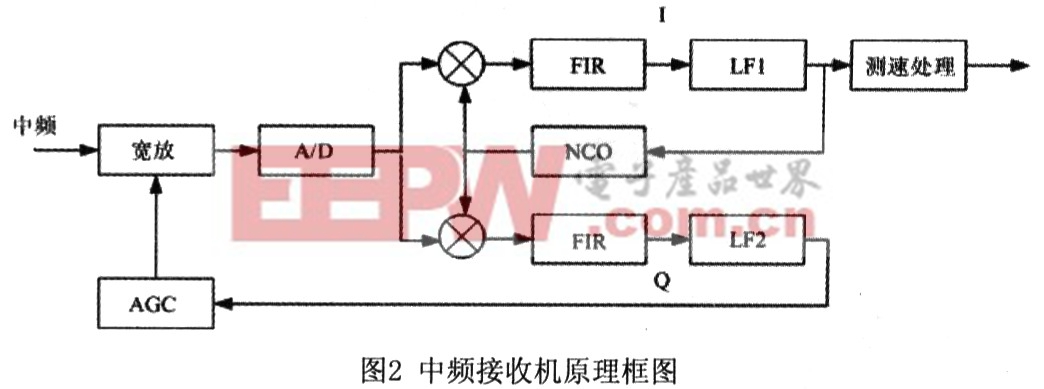

由于受器件水平的制約,數字接收技術目前還難以在射頻頻段直接實現,一般在中頻進行數字化。目前所說的數字測速即是利用中頻數字鎖相環來完成多普勒頻率的提取及測量。數字中頻接收機主要由數字化正交處理單元、數字載波鎖相環和自動增益控制(AGC)環組成。

中頻經A/D采樣后的數字信號與數控振蕩器(NC0)產生的數字正交信號分別進行數字混頻,各經過FIR數字低通濾波器,得到I、Q兩路數字窄帶信號。I、Q兩路信號分別作為數字信號的實部和虛部,做FFT分析,估算出多普勒信息,輸出頻率控制碼控制NCO輸出,實現快速載波頻率引導。I路信號再經過低通濾波器(LF1)完成數字濾波,控制NCO的輸出頻率,從而構成數字鎖相環,在頻率引導成功后實現對載波信號的快速捕獲與跟蹤。環路鎖定后從環路濾波器輸出可以提取出多普勒信息。Q路信號經過一個低通濾波器(LF2),通過I、Q提取輸入信號的幅度信息,實現信號的AGC控制。

3 模塊化設計在FPGA的具體應用

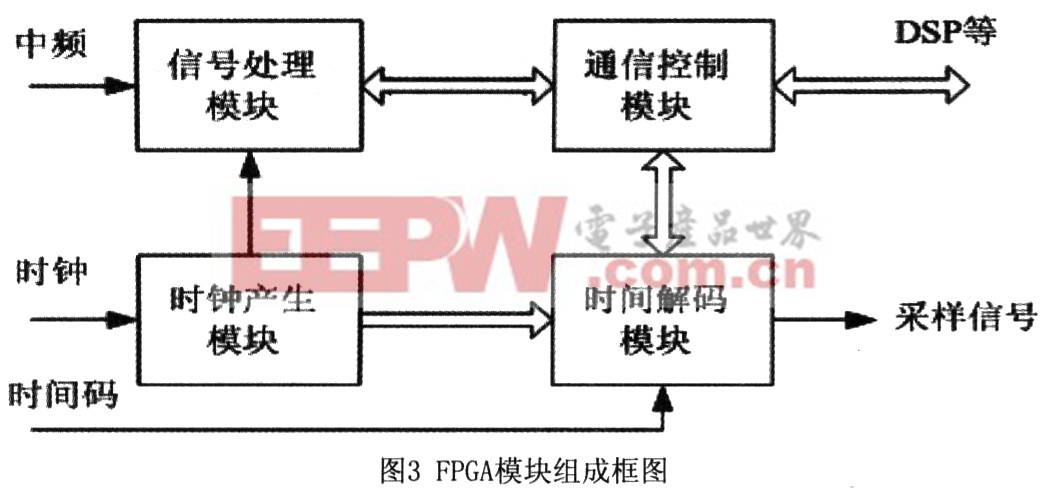

本接收機主要功能是完成連續波雷達的測速和測角任務,設計時在保證指標的前提下,貫徹簡潔至上的原則;并且盡量采用先進、成熟的數字處理技術和軟件無線電技術,貫徹模塊化、通用化、系列化、組合化設計原則,確保系統先進、穩定、可靠。中頻數字接收機是整個接收機部分的核心,設計時遵循簡潔、靈活的特點,盡量減少硬件電路的功能,使其結構簡潔,降低設計和實現的難度,而把復雜的處理交由軟件完成。

評論