FPGA與ADSP TS201的總線接口設計

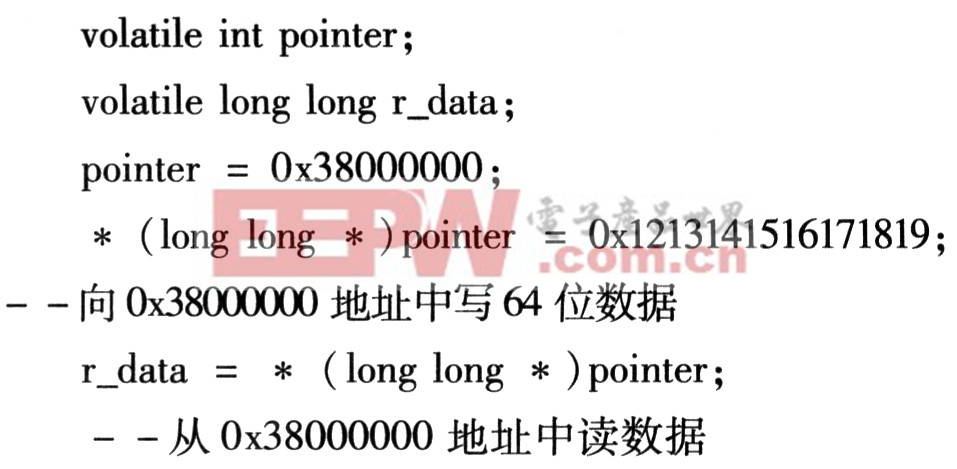

2.3 32位數據總線,64位寄存器

前面提到,突發流水協議與普通流水協議數據傳輸機制是一樣的,只是多了一個指示信號BRST,當寫操作時,FPGA如果在前一時鐘沿采到地址、WRx、BRST信號有效,在下一時鐘沿就鎖存數據到寄存器低位,而如果在前一時鐘沿采到地址、WRL有效,而BRST信號無效,在下一時鐘沿就鎖存數據到寄存器高位。同樣,當讀操作時,FPGA如果采到地址、RD、BRST信號有效,就將寄存器低位驅動到數據總線上,而如果采到地址、RD有效,BRST而信號無效,就將寄存器高位驅動到數據總線上,具體在哪個時鐘沿驅動,由流水深度決定。本文引用地址:http://www.104case.com/article/191872.htm

3 DSP設置

ADSP TS201與FPGA通信時,DSP是否采用流水協議,數據總線位寬,以及流水深度都可以通過系統配置寄存器SYSCON進行設置,SYSCON詳細設置見文獻[3],以32位數據總線訪問64位寄存器為例,一級流水,SYSCON設置為

4 結束語

文中實現了DSP通過外部總線接口訪問FPGA內部寄存器,但是如果需要傳輸的數據量很大,或者DSP與FPGA的時鐘不同步,就不能用寄存器來實現,需要借助于雙口RAM或者FIFO,讀者可以在本文的基礎上加以改進。

評論