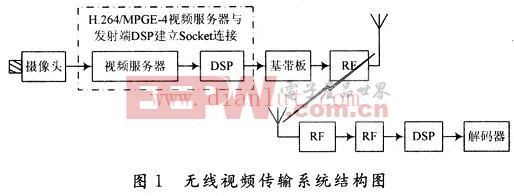

FPGA與ADSP TS201的總線接口設計

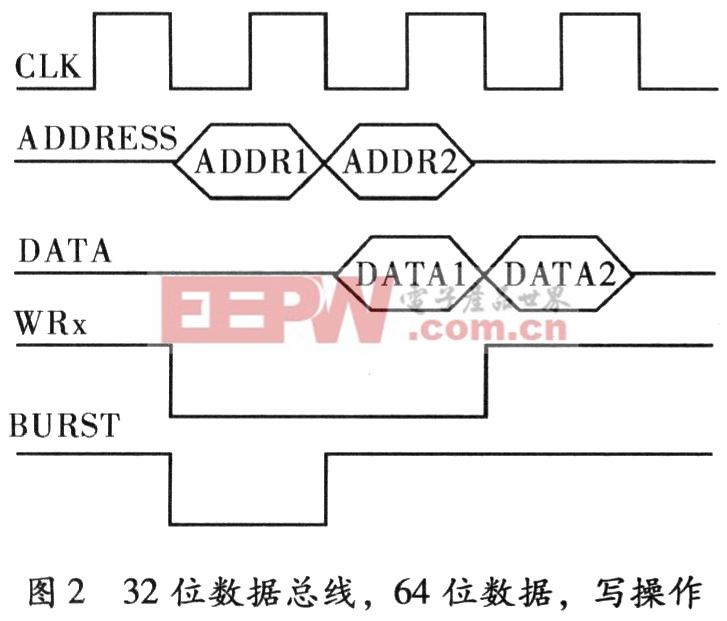

引腳BRST可以用來指示多個傳輸過程合成一個傳輸過程,圖2是DSP通過32位數據總線寫64位數據時序圖。本文引用地址:http://www.104case.com/article/191872.htm

由圖2可以看出,數據傳輸機制與普通流水協議相同,只多了一個BRST指示信號,它與地址1同時有效,表示本次數據沒有傳輸完畢,下次要傳輸的數據與本次傳輸的數據是一個整體,即BRST有效時傳輸是低32位數據,無效時傳輸的是高32位數據,這樣就實現了在32位數據總線上傳輸64位數據,如果沒有BRST信號,該過程會被認為是2次32位傳輸。

同理,如果用32位數據總線傳輸128位數據,在傳輸前3個32位數據的時候,BRST信號有效,傳輸最后一個32位數據BRST無效。

注意:使用流水協議時,流水深度由傳輸類型(讀數據還是寫數據)決定。在寫數據傳輸中,流水深度固定為1;在讀數據傳輸中,流水線深度可由用戶編程決定,即由系統配置寄存器SYSCON決定,在1~4之間可變。

2 FPGA設計

由于DSP的協議是相對固定的,FPGA只需按照協議進行設計即可,下面以DSP訪問FPGA內部寄存器為例詳細介紹。筆者建議采用同步設計,主要信號、輸出信號都由時鐘沿驅動,可以有效避免毛刺。

為了使所設計的模塊通用化,可設流水深度、數據總線位寬、寄存器位寬、寄存器地址可設。筆者建議采用參數化設計,使用參數傳遞語言GENERIC將參數傳遞給實體,在實體內部使用外if…else結構,這樣在一個程序中可以包含各種情況,但不會增加邏輯的使用量。下面以個別情況為例,詳細介紹。

2.1 32位數據總線,32位寄存器,寫操作

前面提過,DSP采用流水協議寫FPGA時,流水深度固定為1,FPGA在前一時鐘沿采到地址、WRx信號有效,在下一時鐘沿就鎖存數據,如圖1所示,FPGA在時鐘沿1采到地址總線上的地址與寄存器地址一致,WRx信號為低,寫標志信號S_W_FLAG置高,由于采用同步設計,FPGA只有在時鐘沿2才能采到S_W_FLAG為高,一旦采到S_W_FLAG為高,FPGA就鎖存數據總線上的數據,即在時鐘沿2鎖存數據。

2.2 32位數據總線,32位寄存器,讀操作

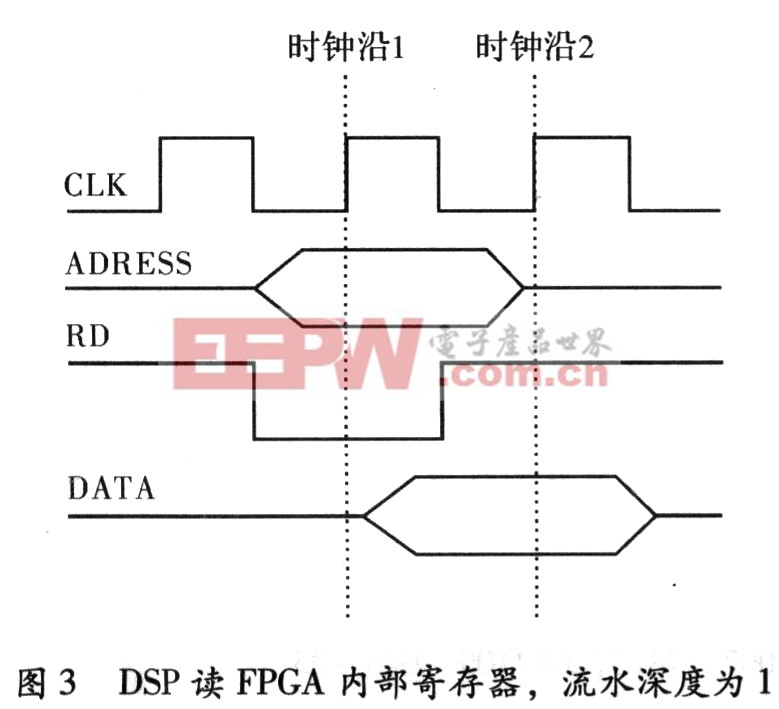

與寫寄存器不一樣,讀寄存器時流水深度在1到4之間可設,需要注意的是,為避免總線沖突,DSP不讀時,FPGA數據總線應保持三態。

如果流水深度設置為1,FPGA在前一時鐘沿采到地址、RD信號有效,應確保在下一時鐘沿數據已經穩定的出現在數據總線上,否則DSP不能正確讀取數據,如圖3所示,在時鐘沿1采到地址總線上的地址與寄存器地址一致,RD信號為低,驅動數據總線,在時鐘沿2數據已穩定出現在數據總線上,DSP可以讀取。

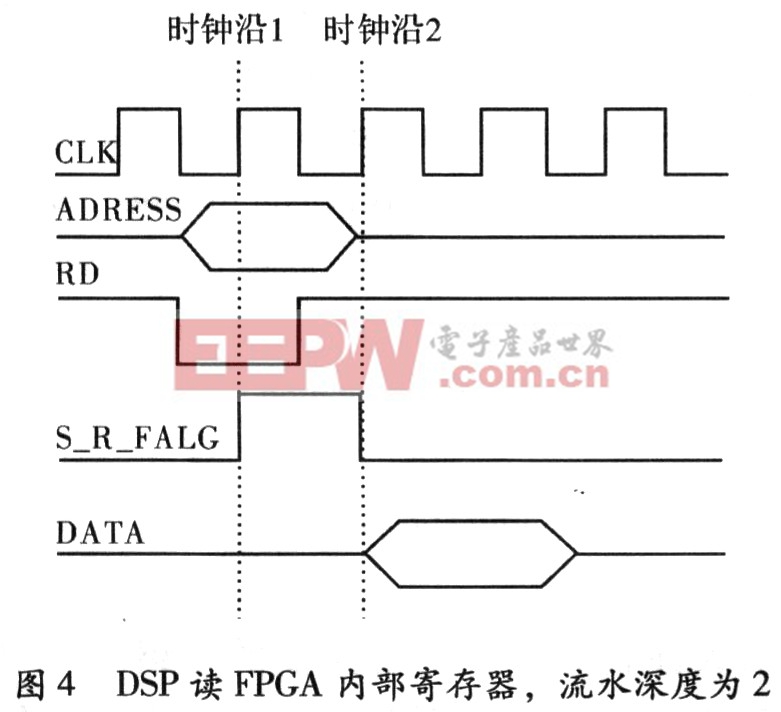

如果流水深度設置為2,FPGA在前一時鐘沿采到地址、RD信號有效,應確保隔一時鐘周期后,數據穩定的出現在數據總線上,這樣就像寫操作一樣,需要加一個標志,當條件滿足,標志為高,一旦標志為高,輸出數據,如圖4所示。

綜上所述,流水深度加深一級,FPGA就晚一個時鐘周期驅動數據總線。可以看出,雖然流水深度在1~4之間可設,但是總能保證一個時鐘周期傳輸一個數據。

評論