基于FPGA的2M誤碼測試儀設計

3.2 時鐘電路

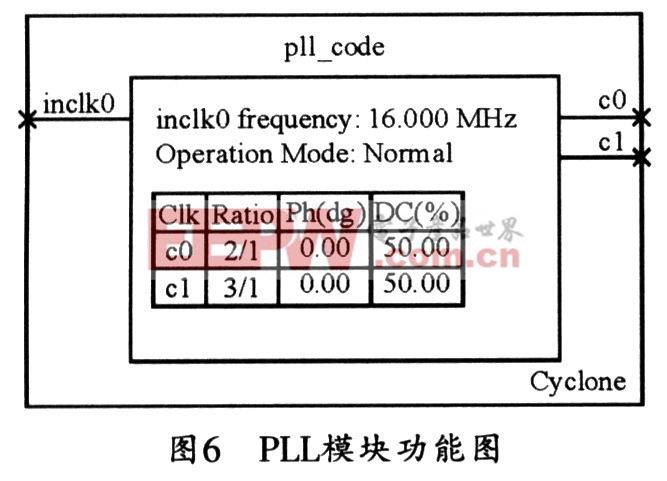

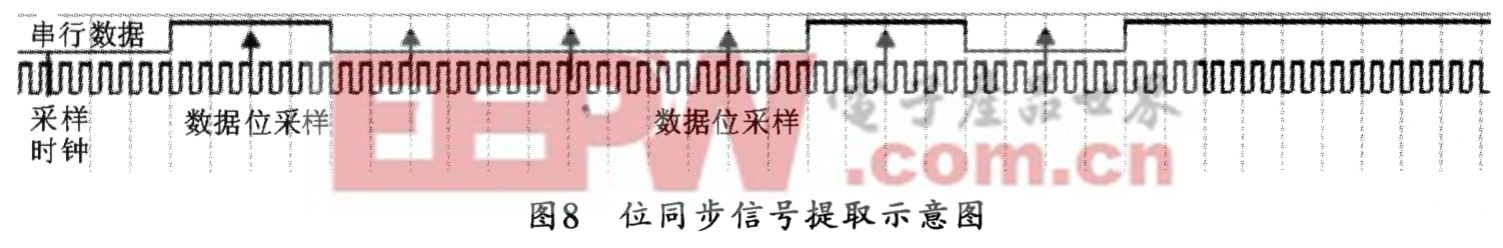

時鐘是整個系統設計中重要的一環。序列發送、序列接收、對E2PROM模塊的讀與寫、串口通信的波特率以及LCD顯示等都離不開時鐘信號的控制,這就需要系統內有一個基準的時鐘模塊來提供所需要的時鐘信號。時鐘模塊可由鎖相環和分頻器模塊構成。通過對QuartusⅡ中mega-function模塊ALTPLL的定制可生成PLL,inclk0是外部有源晶振提供給FPGA的clk0引腳的16 MHz時鐘,可經過PLL產生C0、C1兩個時鐘信號,其中C0是inclk0的2倍,為32 MHz,可作為序列接收模塊中對測試碼進行采樣的采樣時鐘。而C1是inclk0的3倍,為48 MHz,設計時可將C1信號送入分頻電路獲得2 MHz時鐘,作為序列發生器的時鐘;也可將C1信號經分頻電路獲得1 MHz時鐘,作為I2C控制模塊的讀/寫及鍵盤模塊的時鐘信號;當C1信號送入UART控制模塊和LCM控制模塊后,可通過各自模塊內部的分頻電路獲得所需要的時鐘。圖6所示的PLL模塊中方框內表格中的各項內容分別表示信號名稱、信號倍率、信號相位及占空比。本文引用地址:http://www.104case.com/article/191869.htm

3.3 測試序列發送模塊的軟件設計

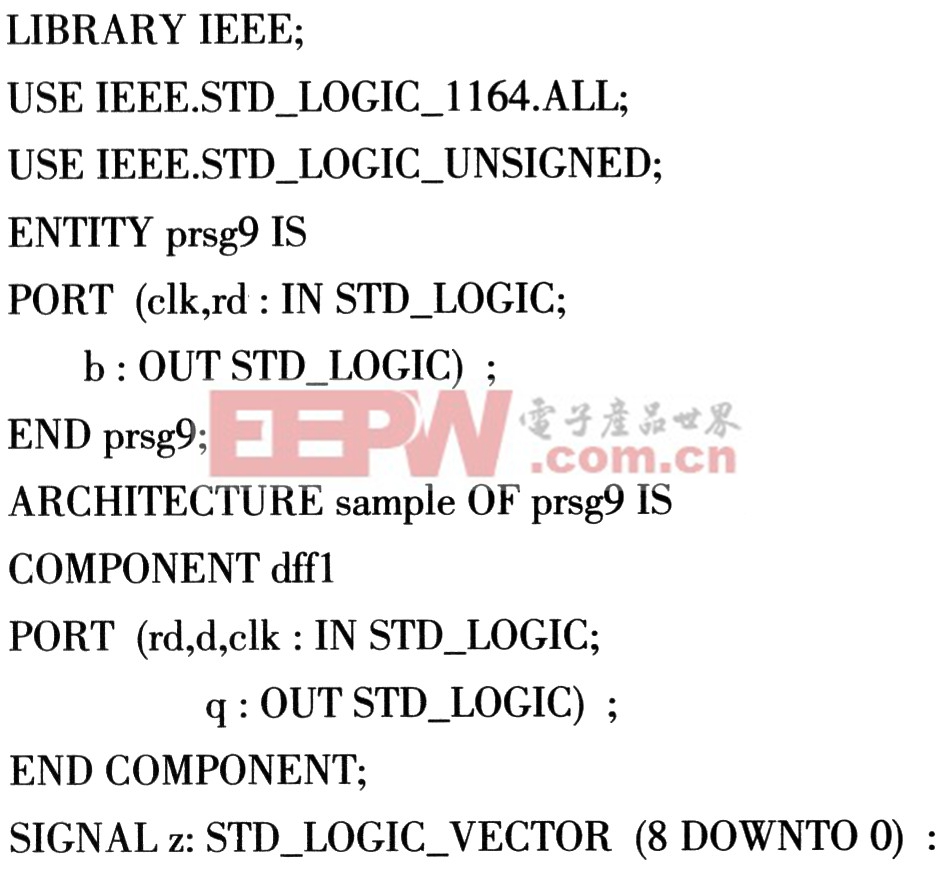

測試序列采用m序列時,ITU建議用于數據傳輸設備測量誤碼的m序列的周期是511,其特征多項式(本原多項式)建議采用f(x)=x9+x5+1,本文應用移位寄存器理論從本原多項式出發來產生m序列,本原多項式是f(x)=x9+x5+1的m序列的VHDL語言編程如下:

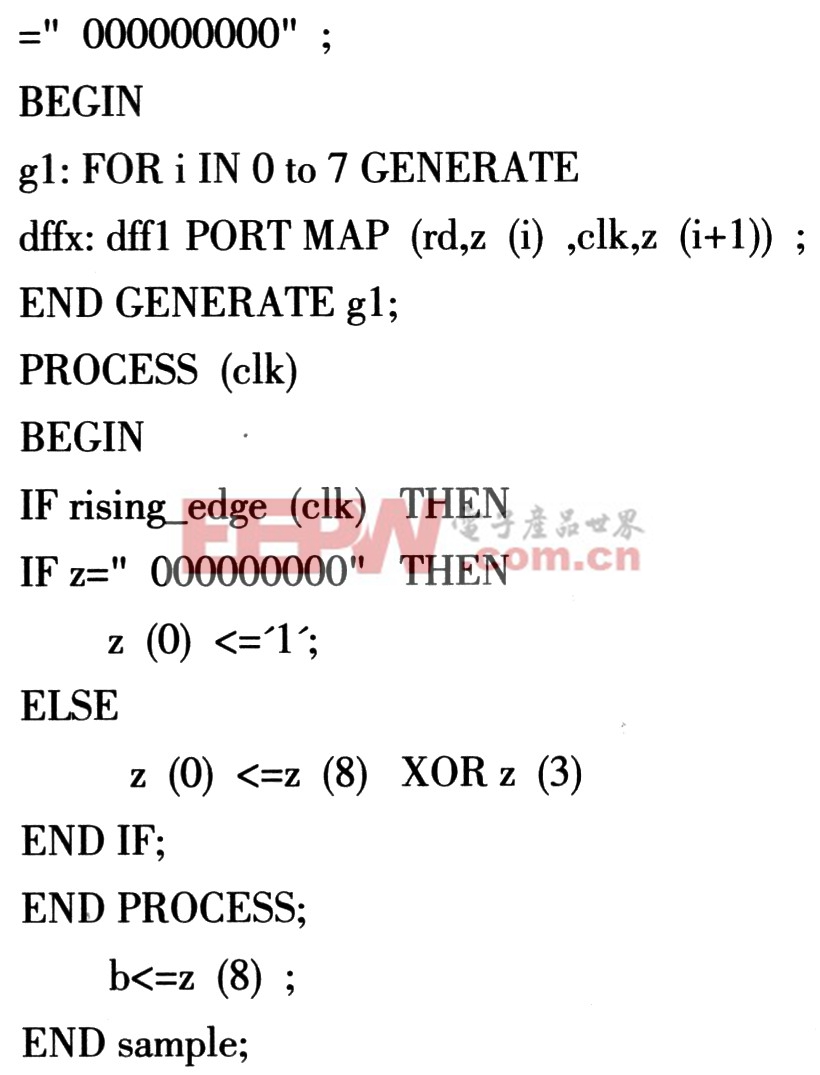

在Ahera的Quaaus II開發平臺下,本原多項式f(x)=x9+x5+1的m序列的仿真波形如圖7所示。

3.5 幀同步信號檢測

對幀同步電路的一項基本要求就是要迅速發現失步,以便及時恢復同步。若在發送端插入幀同步碼“0011011”,那么,在誤碼檢測時,由于E1串行數據流中也會出現“0011011”這樣的內容,因而難以判斷哪些是幀同步碼,哪些是數據內容,所以,在設計中,可采用計數器來進行幀同步碼的定位。

評論