基于802.16d的定時同步算法 改進及FPGA實現

4 基于FPGA的實現

4.1 自相關延時模塊的FPGA實現

為了進一步簡化運算,也可以不進行算法中的歸一化運算,而直接計算R(n)的值,并將公式簡化為:

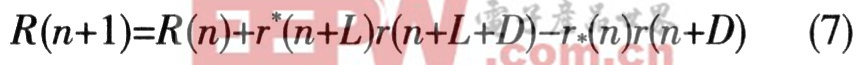

圖3所示是自相關延時模塊的硬件組成結構。它主要由FIFO延時單元、復數運算器、加法器、取模模塊組成。其中復數乘法器可直接使用IP核來實現,這比直接使用四個實數乘法器和兩個加法器更節省資源。本文引用地址:http://www.104case.com/article/191862.htm

將接收端經過下變頻的I路和Q路數據分為兩路送入模塊,I路比Q路數據應多延時一個時鐘周期,這是為了和Q路數據保持相同的時延,此后再進入FIFO經過64個時鐘周期的延時。Q路數據首先進行取相反數運算。這是因為復數共軛運算相當于先取相反數再做復數乘法。把相減的結果送入FIFO進行延時,并將送入系統的復數與做減法和延時64個時鐘周期的復數進行復數乘法運算。由于兩路數據都是16位定點化整數,經過運算后會成為33位,為了節省資源,可將所得結果的高5位和低12位截去,而這并不會影響運算的精度。經過復數乘法運算的實部和虛部再分別經過64個時鐘周期的FIFO延時,并將延時前后的數據做減法運算,然后對計算的結果做累加運算。累加器輸出的結果經過取模模塊后,即可得到實部和虛部的絕對值,然后將兩部分結果相加,再將相加結果與門限值比較,超過門限則將標志位置高。但應注意門限值的選取會影響幀檢測的范圍,由于采用的是聯合檢測方法,應適當擴大門限范圍,本設計設定的門限值為峰值的1/4。

4.2 互相關模塊的FPGA實現

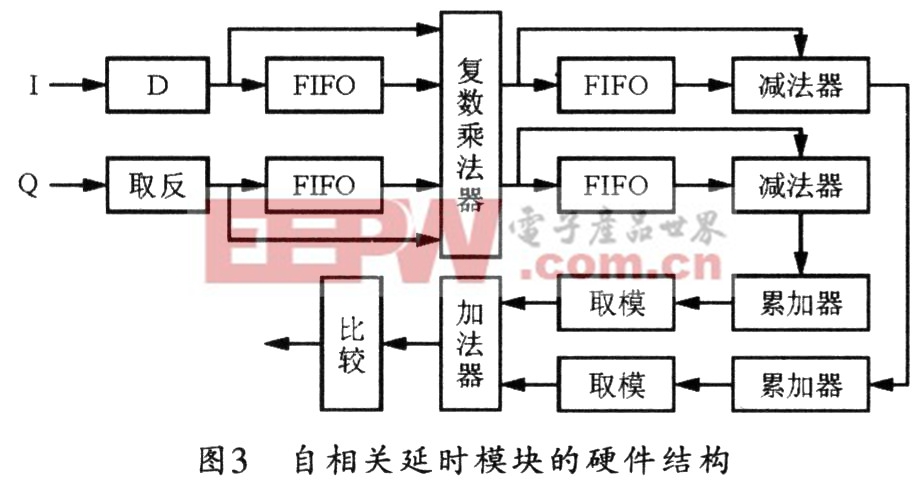

互相關模塊主要由匹配運算單元、取模器和加法器組成。改進的算法只對輸入數據的符號位與本地序列的符號位進行相關運算,并規定輸入符號為正取值為1,輸入符號為負取值為-1,接著根據輸入數據的符號和本地序列的符號構成的16種輸入做全排列,將所有可能的相關運算值算好存放在運算模塊中,這樣就可以根據輸入數據的符號來選擇相關運算的結果。這等效于把復數相關運算簡化為數據選擇器來實現。

圖4所示為互相關模塊的FPGA實現框圖,其中I、Q兩路數據進入模塊后,可取出其最高位存入移位寄存器,然后與本地序列做匹配運算。匹配運算模塊由64個數據選擇器和126個加法器組成,加法運算采用6級流水線來實現,這樣,可使系統的運算速率更高。

4.3 仿真結果分析

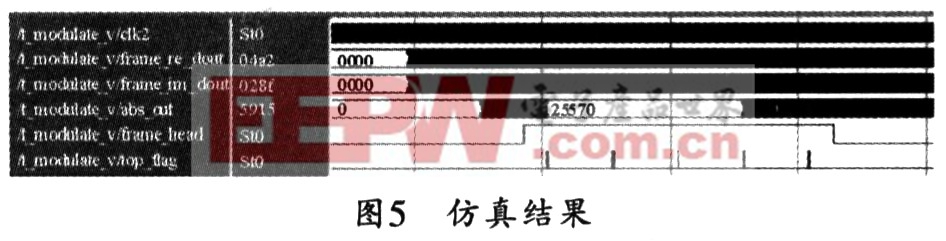

系統中的各模塊可采用Verilog HDL語言設計,并可使用Xilinx公司集成設計環境ISE中的ModelSim SE 6.0來完成仿真,仿真結果如圖5所示。其中frame_re_dout和frame_im_dout為送入系統的實部和虛部數據,abs_out為延時自相關算法中取模相加的結果,frame_head為采用延時自相關算法使數據升高時得到的一個峰值平臺,top_flag為改進自相關算法計算所得的峰值。圖中的自相關平臺內有5個峰值,這與MATLAB仿真結果相符。最后采用Xilinx公司VirtexⅡpro系列xc2vp30器件進行實現。總共邏輯單元使用率為8%,系統最高工作頻率為236.373 MHz 。

5 結束語

本文在研究基于802.16d的OFDM定時同步算法的基礎上提出了一種改進的算法,并在FPGA上完成了其硬件電路設計。仿真結果表明該算法在保持了原算法優秀性能的同時,可節省硬件資源,有利于把同步模塊和接收部分其他模塊集成在單芯片中。同時,該算法也可推廣到具有相似前導字結構的802.1 1a等協議中。

評論