基于802.16d的定時同步算法 改進及FPGA實現

2.2 互相關法

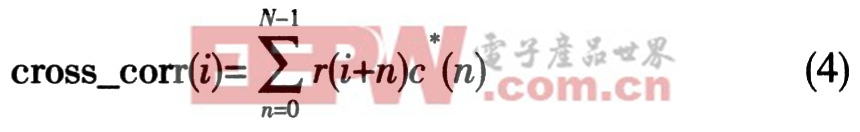

由于IEEE 802.16d協議中的前導字具有良好的互相關特性,故可用已知的訓練序列和接收序列做滑動互相關。當已知的訓練序列和接收的訓練序列恰好對齊時,便會產生一個峰值,峰值對準的位置正是訓練符號的起始點。因此,可以通過尋找互相關的峰值位置來做精確的定時同步。算法公式如下:

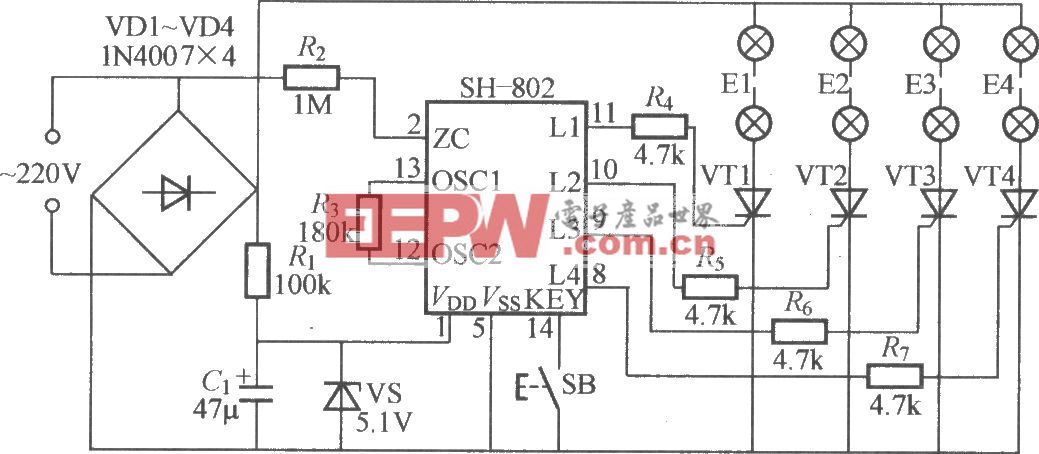

式中,c(n)為短訓練符號在本地的復制樣本,N為短訓練符號的樣值點數。當已知的訓練序列和接收訓練序列恰好對齊時,也會產生一個峰值,其仿真曲線如圖1中的實曲線所示。該算法的缺點是易受頻偏的影響。

根據以上分析,并從算法性能上考慮,若采用延遲自相關法,幀到達時會出現一個峰值平臺,該方法并不能確定幀到達的準確時刻;而采用與本地序列互相關算法又容易受到頻偏的影響而導致定時偏差。本文引用地址:http://www.104case.com/article/191862.htm

3 算法改進

針對上述算法的不足,可對其加以改進,以保證同時具有良好的性能和硬件實現的可行性。改進算法是將兩種算法結合起來進行聯合估計,首先確定一個幀到達的大致平臺,再在這個平臺內找到互相關峰值,如果各個峰值間隔相等,那么可根據最后一個峰值來判斷下一個符號的開始。這種聯合估計的辦法在軟件仿真時具有良好的性能,但若要在硬件上實現則比較困難。因為在延時自相關算法中,計算M(n)的值雖然可采用迭代算法,每次計算只需1次復數運算和若干加法運算;但在自相關計算中,假設接收信號被定點化為16位整數,那么計算一次自相關的值需要16位數據的64次復數乘法,顯然,所需要的硬件資源開銷非常大,而且會影響系統的運行速度。這在硬件上,因資源消耗太大而無法實現。為了兼顧算法的估計精度和實現的復雜性,有必要將算法做進一步改進。即對接收數據進行二階量化以得到d[n]=Q[r(n)],其中Q表示復數量化器,見下式:

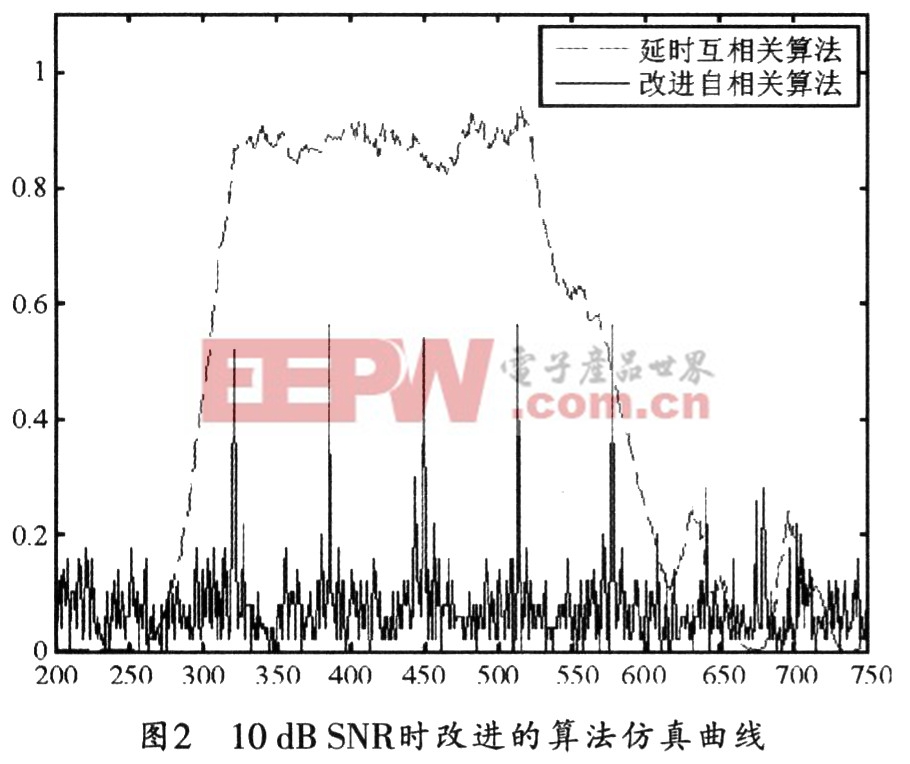

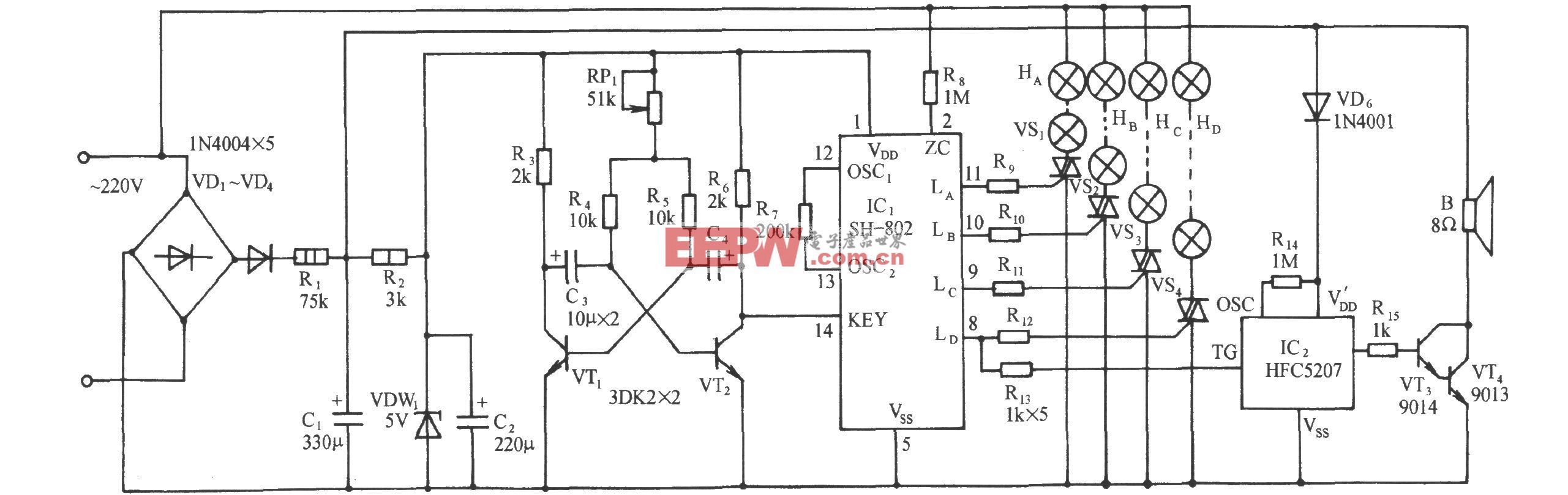

利用這種改進的自相關算法和延時自相關算法進行聯合估計的仿真曲線如圖2所示。

將圖1和圖2進行對比可知,這種對接收數據二階量化的方法會損耗算法的性能,但是,由于幀的大致位置已被限制在一定范圍之內,因此,只需根據峰值就可以確定下一個OFDM符號的準確位置。這種方法既能保證估計精度,又能滿足硬件資源利用率的要求。

評論