基于CycloneII系列FPGA的DDFS信號(hào)源實(shí)現(xiàn)

3 DDFS的FPGA實(shí)現(xiàn)

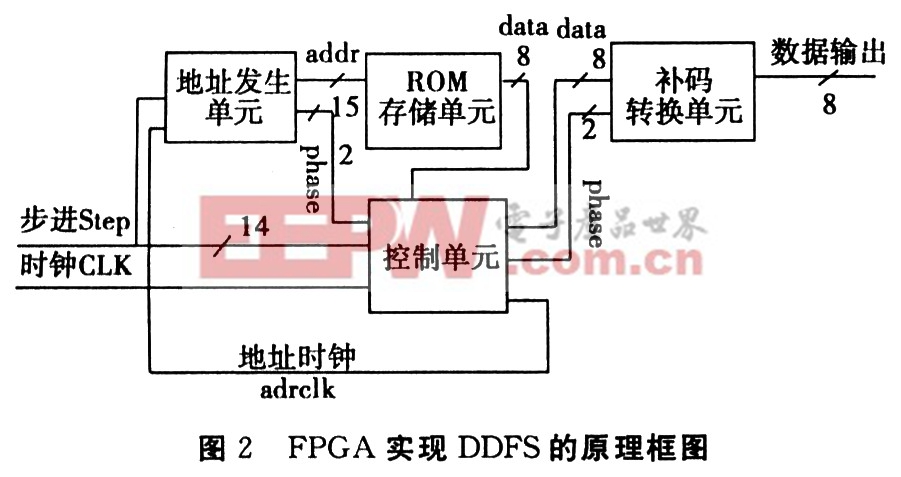

根據(jù)DDFS的原理,其FPGA設(shè)計(jì)原理如圖2所示。其中控制單元由有限狀態(tài)機(jī)構(gòu)成。雖然整個(gè)系統(tǒng)的控制不一定需要使用有限狀態(tài)機(jī),但由于使用的FPGA芯片不支持異步的ROM,即從地址鎖存進(jìn)入ROM單元,到數(shù)據(jù)從ROM中讀出有至少一個(gè)時(shí)鐘周期以上的延時(shí)。因此采用狀態(tài)機(jī)來進(jìn)行控制,可以達(dá)到較好的輸出與時(shí)鐘同步。控制流程為:時(shí)鐘信號(hào)進(jìn)入控制單元,由它產(chǎn)生地址發(fā)生單元的輸入時(shí)鐘adrclk,地址發(fā)生單元在時(shí)鐘adrclk的驅(qū)動(dòng)下,結(jié)合輸入的步進(jìn)信號(hào)Step,產(chǎn)生地址及此地址所對(duì)應(yīng)的象限Phase,此地址產(chǎn)生后立即輸入到ROM單元中,過兩個(gè)時(shí)鐘周期后,控制單元從ROM存儲(chǔ)單元中讀出輸入地址對(duì)應(yīng)的數(shù)據(jù),并在時(shí)鐘的控制下,將前面所產(chǎn)生的象限值Phase與ROM數(shù)據(jù)一起送到補(bǔ)碼轉(zhuǎn)換單元,補(bǔ)碼轉(zhuǎn)換單元根據(jù)Phase的值來決定是否需要進(jìn)行補(bǔ)碼轉(zhuǎn)換,若需要,則進(jìn)行補(bǔ)碼運(yùn)算并將數(shù)據(jù)輸出,若不需要,則直接將數(shù)據(jù)輸出。下面給出各模塊的具體設(shè)計(jì)細(xì)節(jié)。本文引用地址:http://www.104case.com/article/191855.htm

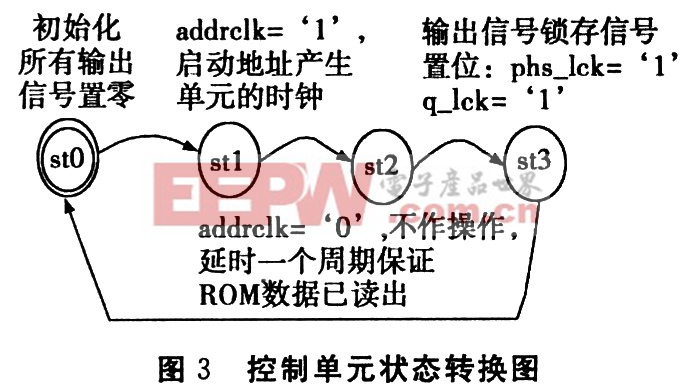

(1)控制單元:控制單元是整個(gè)系統(tǒng)的核心部件。由一個(gè)簡(jiǎn)單的有限狀態(tài)機(jī)構(gòu)成。其狀態(tài)轉(zhuǎn)換圖如圖3所示。

(2)地址發(fā)生單元:設(shè)計(jì)思路為根據(jù)輸入的Step值,計(jì)算出總共四個(gè)象限所需取值的點(diǎn)數(shù),也就可以計(jì)算出一個(gè)象限所要取值的點(diǎn)數(shù)m,然后在時(shí)鐘作用下進(jìn)行計(jì)數(shù),當(dāng)計(jì)數(shù)值達(dá)m個(gè)時(shí),說明一個(gè)象限內(nèi)已經(jīng)取完點(diǎn),此時(shí)phase自加1,計(jì)數(shù)變量重新置零。由于在(0,π/2)sin的函數(shù)值為從0→1變化;(π/2,π)函數(shù)值從1→0變化;(π,3π/2)函數(shù)值從0→-1變化;(3π/2,2π)函數(shù)值從-1→0變化。故在(0,π/2)和(π,3π/2)地址值從0→32767,每隔一個(gè)步進(jìn)Step讀一個(gè)數(shù)據(jù),當(dāng)然后者的數(shù)據(jù)要經(jīng)過補(bǔ)碼單元的處理;而在(π/2,π)和(3π/2,2π)象限,地址值則從32767→0,每隔一個(gè)步進(jìn)Step讀一個(gè)數(shù)據(jù)即可,同樣的,后者的數(shù)據(jù)也要經(jīng)過補(bǔ)碼單元的處理。

(3)ROM存儲(chǔ)單元:ROM存儲(chǔ)單元的數(shù)據(jù)可以通過Matlab進(jìn)行計(jì)算獲得,并將其存儲(chǔ)為*.mif的文件格式。在進(jìn)行ROM設(shè)計(jì)時(shí),調(diào)用此mif文件作為ROM的初始數(shù)據(jù)文件即可。

(4)補(bǔ)碼轉(zhuǎn)換單元:根據(jù)目前地址所處象限來決定是否需要進(jìn)行補(bǔ)碼轉(zhuǎn)換。如產(chǎn)生正弦信號(hào)時(shí),(0,π)象限sin函數(shù)值為正,而(π,2π)象限上sin函數(shù)值為負(fù),因此在(π,2π)象限時(shí),需要對(duì)輸出數(shù)據(jù)進(jìn)行補(bǔ)碼轉(zhuǎn)換。補(bǔ)碼轉(zhuǎn)換單元較簡(jiǎn)單,根據(jù)二進(jìn)制數(shù)取補(bǔ)的原理進(jìn)行設(shè)計(jì)即可。

評(píng)論