一種可編程的全數字鎖相環路的實現

鎖相環路已在模擬和數字通信及無線電電子學等各個領域中得到了極為廣泛的應用,特別是在數字通信的調制解調和位同步中常常要用到各種各樣的鎖相環。鎖相就是利用輸入信號與輸出信號之間的相位誤差自動調節輸出相位使之與輸入相位一致,或保持一個很小的相位差。最初的鎖相環全部由模擬電路組成,隨著大規模、超高速數字集成電路的發展及計算機的普遍應用,出現了全數字鎖相環路。所謂全數字鎖相環路,就是環路部件全部數字化,采用數字鑒相器(DPD)、數字環路濾波器(DLF)、數控振蕩器(DCO)構成鎖相環路。在用Altera公司的EPFl0K10TCl44-3芯片設計一種無線通信實驗系統的FSK、DPSK、QAM調制解調器時,利用剩余的10%FPGA資源設計出了一種可編程全數字鎖相環路,它成功地為該通信實驗系統的調制解調器提供了64kHz、56kHz和16kHz三種精確、穩定的時鐘信號。

本文引用地址:http://www.104case.com/article/191850.htm1 全數字鎖相環的電路設計

1.1 DPLL工作原理分析

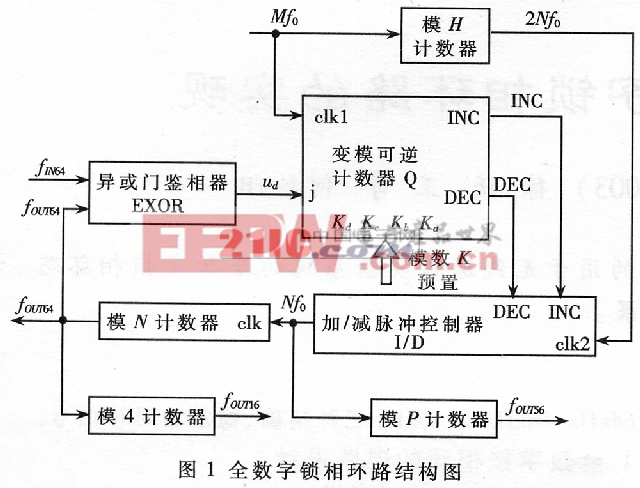

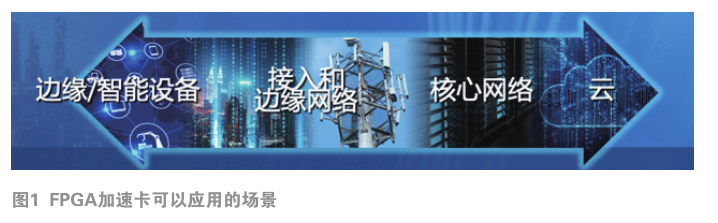

所設計的全數字鎖相環路的結構如圖1所示。其中,數字鑒相器由異或門EXOR構成,數字環路濾波器由變模可逆計數器Q構成,數控振蕩器由加/減脈沖控制器I/D和模N計數器組成。可逆計數器和加/減脈沖控制器的時鐘頻率分別是Mf0和2Nf0。這里f0是環路的中心頻率,為64kHz。Mf0等于14336kHz,由晶振電路產生,它經模H計數器分頻后得到2Nf0的時鐘頻率。異或門鑒相器用于比較輸入信號IN64與數控振蕩器輸出信號OUT64的相位差,其輸出信號ud作為可逆計數器的計數方向控制信號。當ud為低電平時,可逆計數器作“加”計數;反之,可逆計數器作“減”計數。當環路鎖定時,IN64和OUT64正交,鑒相器的輸出信號ud為50%占空比的方波。在這種情況下,可逆計數器“加”與“減”的周期相同,只要可逆計數器的模值K足夠大(K>M/4),其輸出端就不會產生進位或借位脈沖。這時,加/減脈沖控制器只對頻率為2Nf0的時鐘進行二分頻,使IN64和OUT64的相位保持正交。在環路未鎖定的情況下,若ud為低電平時,可逆計數器進行加計數,并產生進位脈沖作用到加/減脈沖控制器的“加”控制端INC,該控制器便在二分頻過程中加入半個時鐘周期;反之,若ud為高電平,可逆計數器進行減計數,并產生借位脈沖作用到加/減脈沖控制器的“減”輸入端DEC,該控制器便在二分頻的過程中減去半個時鐘周期,這個過程是連續發生的。加/減脈沖控制器的輸出經過模N計數器分頻后,得到輸出信號OUT64,它的相位不斷受到調整控制,最終達到鎖定狀態。最后只要對OUT64進行4分頻就能得到16kHz的輸出信號OUTl6,對加/減脈沖控制器的輸出進行P分頻就能得到56kHz的輸出信號OUT56。

圖1

該全數字鎖相環的三個輸出信號的頻率分別為64kHz、56kHz和16kHz,經過計算可確定鎖相環的參數M、N和P。設H=8,因為Mf0=14336kHz=4×4×2×7×64kHz,故M=4×4×2×7=224。因為2Nf0=Mf0/H=4×4×2×7×64kHz/8=2×2×7×64kHz=2×2×8×56kHz,故N=14、P=16。

數字通信相關文章:數字通信原理

塵埃粒子計數器相關文章:塵埃粒子計數器原理 鑒相器相關文章:鑒相器原理 數字濾波器相關文章:數字濾波器原理 鎖相環相關文章:鎖相環原理 鎖相放大器相關文章:鎖相放大器原理 網線測試儀相關文章:網線測試儀原理

評論