基于FPGA的作戰(zhàn)系統(tǒng)時統(tǒng)設計

其中CLK(時鐘)、RST(復位)、A(外部授時信號)、B(自產生信號)為輸入信號。Y為輸出信號,即中斷信號。仿真結果如圖4所示。本文引用地址:http://www.104case.com/article/191848.htm

4 時間精度

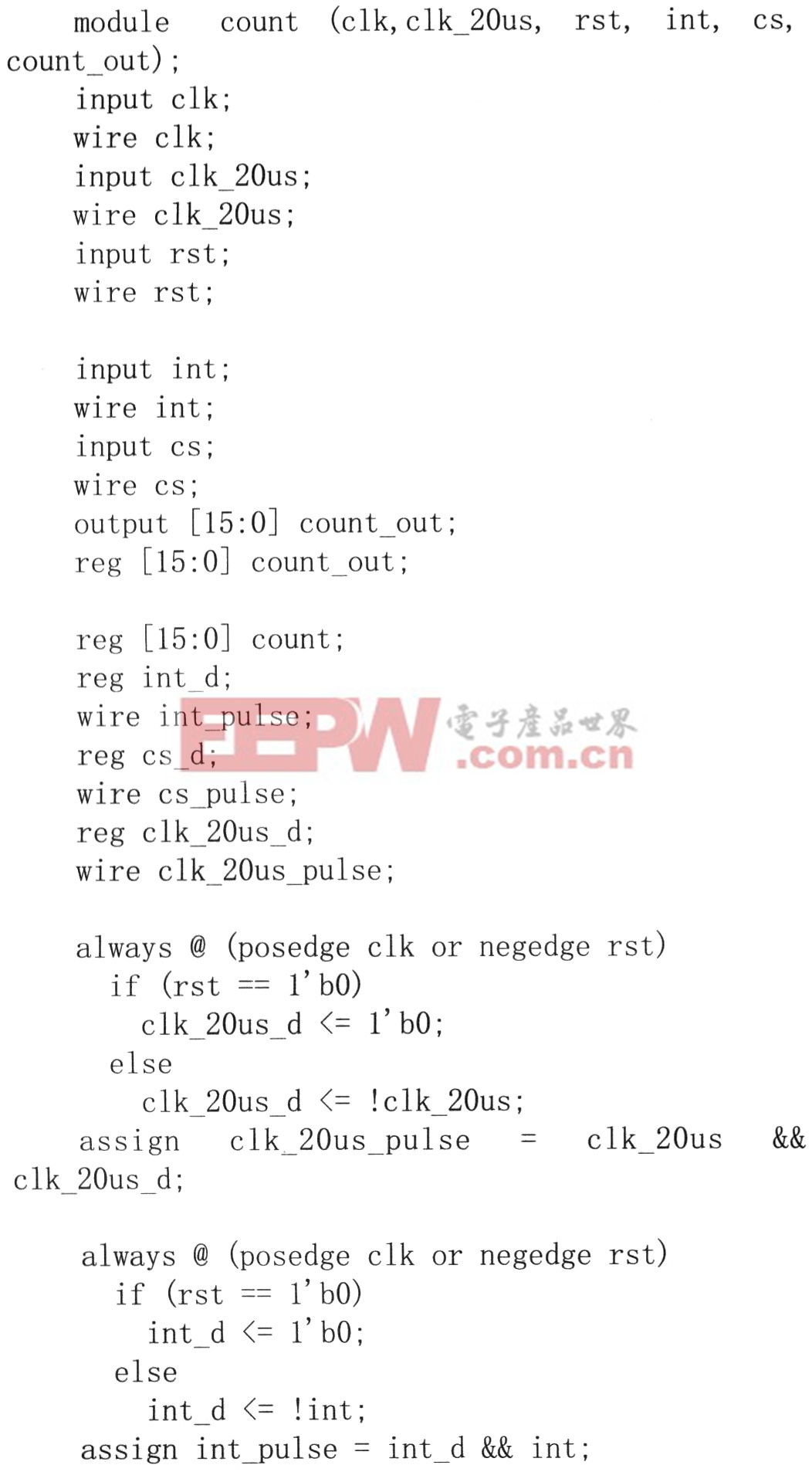

外部授時信號大多為1秒周期的秒脈沖信號,這時系統(tǒng)獲得的時間只能精確到秒。在需要獲得精確度更高的時間信息時,可利用FPGA中的計數器等來實現設計。見下面所示:

其中clk(時鐘)、clk_20μs(20μs周期時鐘)、rst(復位)、int(外部信號)、cs(鎖存當前計數值)為輸入信號。count_out為輸出的16位二進制計數值(eount out[15..0])。本功能能夠給出20μs精度的計數,在秒脈沖到來時(上升沿)產生中斷,同時啟動計數器,為20μs一次的計數,最大計數值為50000。計數值存入寄存器,可隨時讀取當前計數值,得出計數值后可換算成ms等其它值。其仿真結果如圖5所示。

5 結束語

利用FPGA完成了作戰(zhàn)系統(tǒng)對時統(tǒng)模塊功能要求的設計,經在工程項目中使用驗證,其功能完全滿足要求。設計中使用的FPGA(EPM7256SRl208一lO)是一種高性能的CMOS EEPROM器件,通過4個引腳的JTAG接口能夠進行在線編程,在開發(fā)過程中實現了快速有效的重復編程。借助其可重復編程使用的靈活性,通過改寫FPGA內部邏輯來實現不同的功能需求,避免了硬件的重復設計,縮短了設計周期,適應了發(fā)展的需要。

評論