基于FPGA的簡易數字存儲示波器設計

3 FPGA程序設計

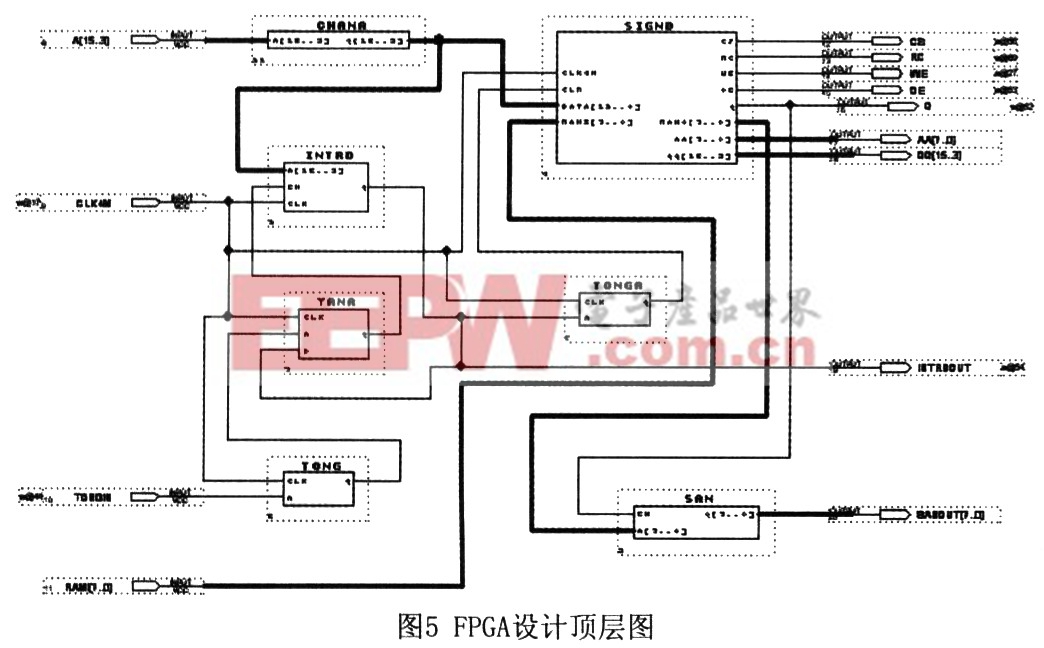

此部分實現的主要的功能是將A/D轉換后的數據經FPGA控制寫入RAM及將數據從RAM讀出經FPGA輸出給D/A轉換器,頂層原理圖如圖5所示。外圍主要接口端功能為:A[15..3]為數據輸入端,CLK4M為時鐘信號端,TONGIN為觸發端口,CS、RC、WE、OE為片選、轉換、讀寫控制端,RAMI、RAMO、AA為存儲器I/O端、地址端,QQ為數據輸出端。

其中模塊CHANA實現的功能是對數據的最高位取反,因為AD976最高位“l”表示負電平,而AD669最高位“1”表示高電平;模塊INTRD在EN為“1”,信號上升沿過零點時,Q輸出為“l”,直到完成對存儲器的寫操作為止;模塊SIGND是整個程序的核心部分,主要功能是為存儲器和lAD976提供控制信號,啟動A/D轉換,對存儲器進行寫操作和讀操作;模塊SAN在對存儲器由寫操作轉變為讀操作后,將存儲器的數據輸出變為高阻態,不妨礙存儲器數據的正常讀入;模塊TONG端口A外接開關,按下時低電平,起同步作用。仿真結果如圖6,(a)為寫操作時的仿真波形;(b)為讀操作時的仿真波形。當運行在寫操作時,QQ無輸出,如圖6(a)所示,實現存儲功能,讀操作時,QQ輸出,由于模塊CHANA的存在,QQ輸出的數據要對A輸入的數據首位取反,即A輸入是0101,QQ輸出是1101,如圖6(b)所示,仿真結果正確。

4 結語

本文以PLC器件為控制核心,通過附加一定的外電路及普通示波器構成簡易數字存儲器,使普通示波器具有波形數字存儲的功能。其中以FPGA為主部件的控制部分采用VHDL語言,按模塊化方式進行設計,并將各模塊集成于芯片中,最后通過MAXPLUS II軟件對設計進行邏輯仿真,對FPGA芯片進行編程,實現系統的設計要求。隨著科學技術的不斷發展,這種以FPGA為基礎的軟件硬件化,其發展前景十分看好。

評論