基于FPGA“乒乓球比賽游戲機”的設計

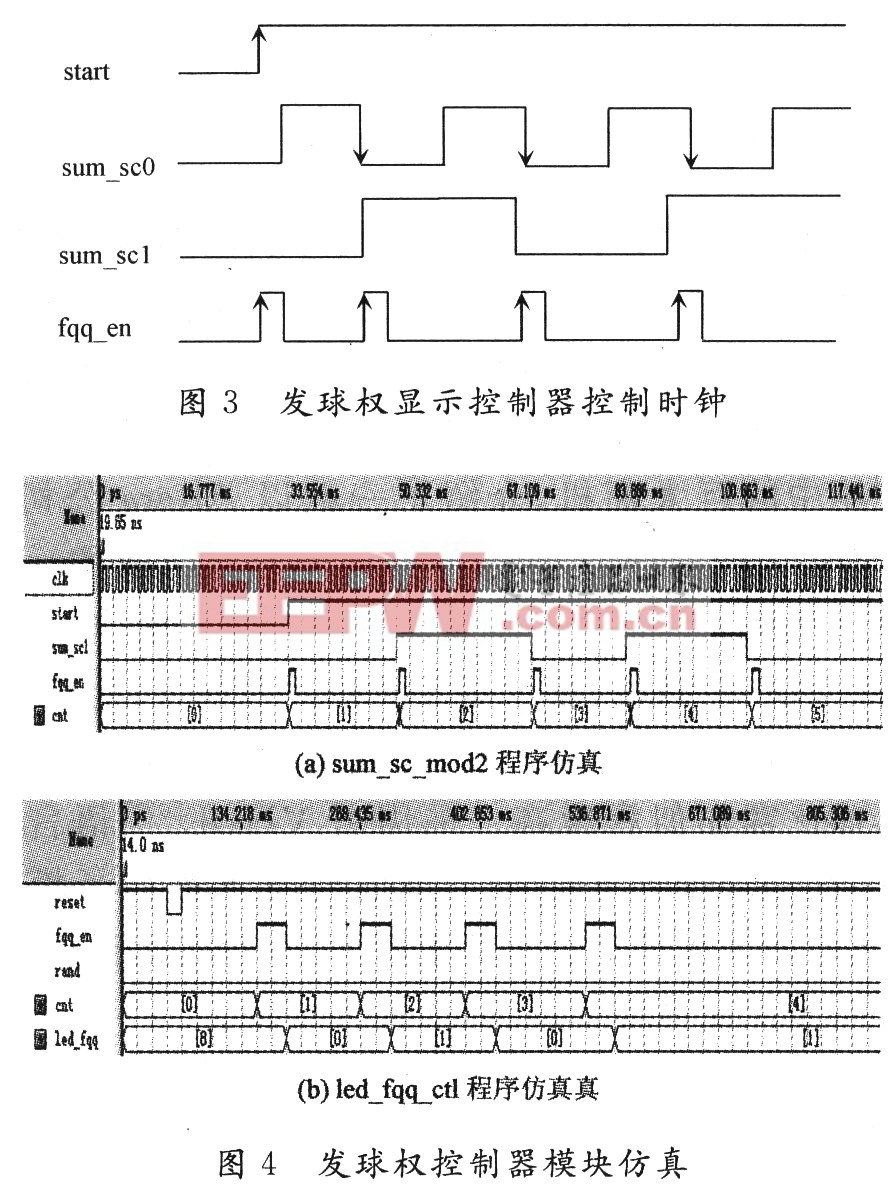

此模塊設計中,發球權數碼管的信號控制受多個時鐘的控制,即開始比賽開關start和計分值sum_sc0信號,這在VHDL編程語言中無法用一個進程實現,必須將兩個信號組合成一個時鐘信號,并統一兩個時鐘的觸發沿。因此最佳時鐘觸發方式如圖3所示的fqq_en信號。為滿足這種時序要求,借助計分總和次低位sum_sc1信號設計entity sum_sc_mod2,由于start和sum_sc1的頻率都遠低于系統時鐘信號clk頻率,則可借助clk高頻信號捕捉其邊沿產生新的時鐘信號fqq_en,并產生其計數值,仿真波形如圖4(a)所示。為保證發球權數碼管顯示正確,設計entitv led_fqq_ctl在fqq_en下降沿時,根據其計數值產生相應的數碼管輸出信號led_fqq,仿真波形如圖4(b)所示。本文引用地址:http://www.104case.com/article/191845.htm

發球權控制器的VHDL核心程序如下:

評論