基于FPGA技術(shù)的數(shù)字相關(guān)器的設(shè)計與實現(xiàn)

3 用VHDL設(shè)計數(shù)字相關(guān)器

用VHDL設(shè)計數(shù)字相關(guān)器的邏輯框圖如圖2所示。

圖2 字相關(guān)器的邏輯框圖

本文用VHDL設(shè)計的數(shù)字相關(guān)器,僅需一個數(shù)據(jù)時鐘,避免了復(fù)雜的時序控制,它采用適時運算處理,所得相關(guān)峰的寬度是一個數(shù)據(jù)比特,比較容易捕獲,不會產(chǎn)生丟峰漏峰等不良現(xiàn)象,提高了相關(guān)器的可靠性。

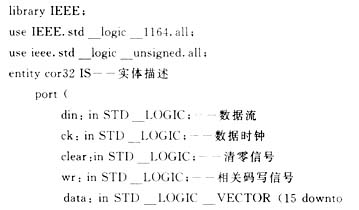

下面給出32-bit數(shù)字相關(guān)器的部分VHDL源程序。

4 FPGA實現(xiàn)32-bit數(shù)字相關(guān)器

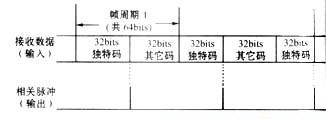

本設(shè)計選用XC4044XLA FPGA芯片實現(xiàn),開發(fā)工具是XILINX公司的FoundationSeries3.1i。相關(guān)器僅占該芯片部分資源,該芯片其余資源為同步系統(tǒng)中其它部件所用。 下面給出該相關(guān)器測試結(jié)果。給相關(guān)器設(shè)置32位相關(guān)碼:將0F7ADH、96E8H依次由低到高置入相關(guān)碼寄存器中,其接收數(shù)據(jù)中的獨特碼與相關(guān)碼相同,測試結(jié)果如圖3所示。

圖3測試結(jié)果

5 結(jié)束語

用VHDL設(shè)計在FPGA芯片中實現(xiàn)數(shù)字相關(guān)器,簡化了相關(guān)器復(fù)雜的邏輯電路設(shè)計,降低了相關(guān)器的功耗,提高了相關(guān)器的可靠性。該相關(guān)器已成功地應(yīng)用于某無線通信系統(tǒng)中,性能穩(wěn)定可靠。

超級電容器相關(guān)文章:超級電容器原理

評論