基于高端FPGA的IC驗證平臺的PI分析

多節點仿真通過將電源平而分隔成用戶定義的網絡尺寸,并將VRM噪聲源以及去耦電容連在網格中合適的節點,通過確定每個節點附近的阻抗來進行更精確的仿真。

為使仿真最準確,網格中網孔的大小必須大于系統最高頻率對應波長的1/10。系統的最高工作頻率為266MHz(DDR內存模塊),電路板電介質材料是FR-4,介電常數εr為4.5,于是波長如下:

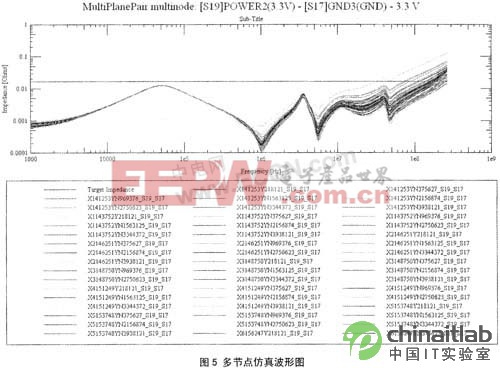

電路板大小為122mm×205mm,故只需4×4的網格就可以準確仿真。為便于分析,本文采用8×8的網格。放置好電容后,多節點仿真結果如圖5所示。

|

在0-266MHz之間,波形大部分都在目標阻抗以下,超出目標阻抗的波形所代表的網孔都在電路板的邊緣,對電路影響不大,因此電容分布滿足要求。

4 總結

通過電路的實際測量,發現各電源分配系統均能很好的工作,與仿真結果基本一致。為了進一步提高仿真精度,可以通過頻域測試,建立基于S參數或SPICE等效電路的電容模型庫,也有利于提高電源完整性仿真的效率。

本文討論的系統是FPGA的IC設計驗證平臺,其電源完整性的分析方法對于其他類型的電子產品設計也有一定的借鑒意義。隨著系統頻率的提高,電源分配系統越來越復雜,PCB的電源地阻抗諧振現象變得更加突出,直接影響到系統的穩定工作以及產品級的EMI/EMC認證,因此在IC或產品設計早期,應該在系統層面進行電源完整性仿真,模擬真實系統的行為,提前發現系統中潛在的電源問題,從而有利于提高產品系統工作的穩定性,加快產品的開發上市。

評論