用中檔FPGA實現高速DDR3存儲器控制器

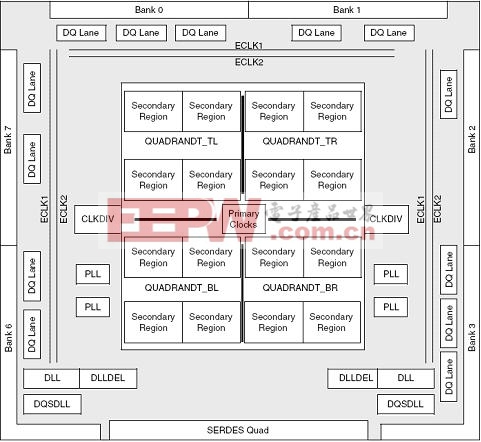

LatticeECP3 FPGA的I/O有專門的電路支持高速存儲器接口,包括DDR、DDR2和DDR3 SDRAM存儲器接口。如圖3所示,ECP3系列還有專用的時鐘資源,以支持下一代DDR3高速存儲器控制器。邊緣時鐘(ECLK1,ECLK2)是高速,低相偏的時鐘,用于時鐘控制數據高速地進出器件。在DQS的通道提供時鐘輸入(DQS)和與該時鐘相關的多達10個輸入數據位。DQSBUF服務于每個DQS通道,以控制時鐘訪問和延遲。DQSDLL支持DQS通道(每個器件的左側和右側都有一個)。DQSDLL是專門用于構建90度時鐘延遲的DLL。

圖3 LatticeECP3 DDR存儲器時鐘資源

萊迪思的DQS電路包括一個自動時鐘轉換電路,簡化了存儲器接口設計,并確保了可靠的操作。此外,DQS的延遲塊提供了針對DDR存儲器接口所需的時鐘對齊。通過DQS的延遲單元至專用的DQS布線資源,向PAD提供DQS信號。溫度,電壓和工藝變化對專用DQS延遲塊產生的差異由設置的校準信號來補償(7位延遲控制),校準信號源于器件對邊的兩個DQSDLL。在器件的一半,每個DQSDLL彌補各自邊的DQS延遲。通過系統時鐘和專用反饋環路,對DLL環進行了補償。

LatticeECP3 FPGA的鎖相環用于生成針對DDR3存儲器接口時鐘。例如,對于一個400 MHz的DDR3接口,通用鎖相環用于生成三個時鐘:400 MHz的時鐘,有90 °相移的400 MHz時鐘和200 MHz時鐘。有90 °相移的400 MHz時鐘用于生成DQ和DQS輸出。沒有相移的400 MHz時鐘用于產生時鐘(CLKP和CLKN)到DDR3存儲器。200 MHz時鐘用于生成地址和命令(ADDR/CMD)信號。該時鐘的實現對客戶是透明的,可用萊迪思的設計工具自動地實現。

DDR3所需的寫調整是通過使用動態延遲輸入至專門的DDR3存儲器接口的模塊,這稱為DQSBUFD模塊。這個DQSBUFD模塊包含了DQS延遲塊,時鐘極性控制邏輯和數據有效模塊。DDR3所需的寫調整是通過使用動態延遲(DYNDELAY)輸入DQSBUFD模塊。根據寫調整的要求,可以延遲每個DQS組的輸出。

評論