用中檔FPGA實現高速DDR3存儲器控制器

引言

本文引用地址:http://www.104case.com/article/191805.htm由于系統帶寬不斷的增加,因此針對更高的速度和性能,設計人員對存儲技術進行了優化。下一代雙數據速率(DDR)SDRAM芯片是DDR3 SDRAM。 DDR3 SDRAM具有比DDR2更多的優勢。這些器件的功耗更低,能以更高的速度工作,有更高的性能(2倍的帶寬),并有更大的密度。與DDR2相比,DDR3器件的功耗降低了30%,主要是由于小的芯片尺寸和更低的電源電壓(DDR3 1.5V而DDR2 1.8V)。 DDR3器件還提供其他的節約資源模式,如局部刷新。與DDR2相比,DDR3的另一個顯著優點是更高的性能/帶寬,這是由于有更寬的預取緩沖(與4位的DDR2相比,DDR3為8位寬),以及更高的工作時鐘頻率。然而,設計至DDR3的接口也變得更具挑戰性。在FPGA中實現高速、高效率的DDR3控制器是一項艱巨的任務。直到最近,只有少數高端(昂貴)的FPGA有支持與高速的DDR3存儲器可靠接口的塊。然而,現在新一代中檔的FPGA提供這些塊、高速FPGA架構、時鐘管理資源和需要實現下一代DDR3控制器的I/O結構。本文探討設計所遇到的挑戰,以及如何用一個特定的FPGA系列LatticeECP3實現DDR3存儲器控制器。

DDR3存儲器控制器的挑戰

針對存儲器控制器,DDR3器件面臨一系列的挑戰。DDR3的工作頻率起始于DDR2的更高的工作頻率,然后趨于更高的頻率。 DDR3接口需要的時鐘速度超過400 MHz。這是對FPGA架構的一個重大挑戰。針對DDR3存儲器控制器的架構,fly-by結構和讀寫調整變得更加復雜。

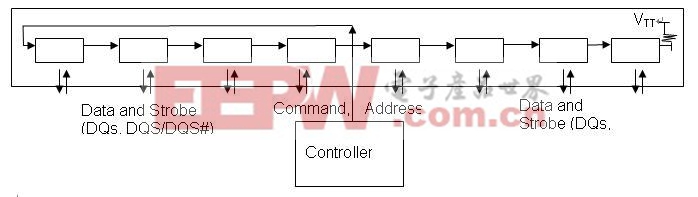

圖1 針對DDR3的Fly-by結構

不同于DDR2的T型分支拓撲結構,DDR3采用了fly-by拓撲結構,以更高的速度提供更好的信號完整性。fly-by信號是命令、地址,控制和時鐘信號。如圖1所示,源于存儲器控制器的這些信號以串行的方式連接到每個DRAM器件。通過減少分支的數量和分支的長度改進了信號完整性。然而,這引起了另一個問題,因為每一個存儲器元件的延遲是不同的,取決于它處于時序的位置。通過按照DDR3規范的定義,采用讀調整和寫調整技術來補償這種延遲的差異。fly-by拓撲結構在電源開啟時校正存儲器系統。這就要求在DDR3控制器中有額外的信息,允許校準工作在啟動時自動完成。

讀和寫調整

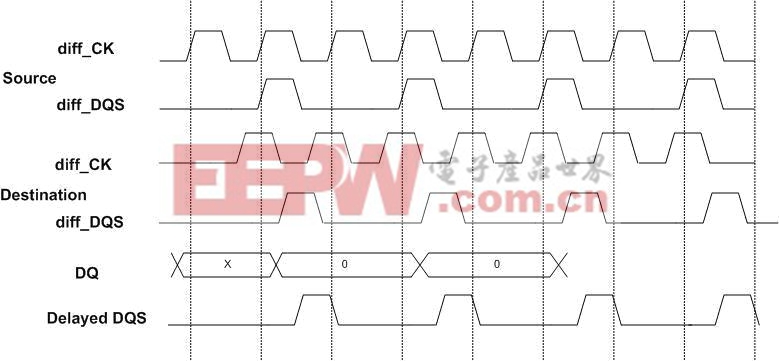

在寫調整期間,存儲器控制器需要補償額外的跨越時間偏移(對每個存儲器器件,信號延遲是不同的),這是由于fly-by拓撲結構及選通和時鐘引入的。如圖2所示,源CK和DQS信號到達目的地有延遲。對于存儲器模塊的每個存儲器元件,這種延遲是不同的,必須逐個芯片進行調整,如果芯片有多于一個字節的數據,甚至要根據字節來進行調整。該圖說明了一個存儲器元件。存儲器控制器延遲了DQS,一次一步,直到檢測到CK信號從0過渡到到1。這將再次對齊DQS和CK,以便DQ總線上的目標數據可以可靠地被捕獲。由于這是由DDR3存儲器控制器自動做的,電路板設計人員無須擔心實施的細節。設計人員會從額外的裕度中得到好處,這是由DDR3存儲器控制器中的寫調整的特性所創建的。

圖2 寫調整的時序圖

評論